SNIA I SFF

# SFF-TA-1039

Specification for

# **PCIe OptiLink Hardware and Electrical Specifications**

Rev 0.0.3

October 1, 2025

Chairman SFF TWG

Email: SFF-Chair@snia.org

SECRETARIAT: SFF TWG

This specification is made available for public review at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Comments may be submitted at <a href="https://www.snia.org/feedback">https://www.snia.org/feedback</a>. Comments received will be considered for inclusion in future revisions of this specification.

This document has been released by SNIA. The SFF TWG believes that the ideas, methodologies, and technologies described in this document are technically accurate and are appropriate for widespread distribution.

The description in this specification does not assure that the specific component is available from suppliers. If such a component is supplied, it should comply with this specification to achieve interoperability between suppliers.

ABSTRACT: This specification defines the contact pads, the electrical, power supply, ESD and thermal characteristics of the PCIe front panel pluggable (FPP) 4x, 8x, and 16x module or cable plug called OptiLink addressing compute and AI scale-up networks. This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules.

POINTS OF CONTACT: SNIA Technical Council Administrator

Email: TCAdmin@snia.org

EDITORS: Ali Ghiasi, Molex, LLC

Email: ali.ghiasi@molex.com

**PCIe OptiLink Hardware and Electrical Specifications**

#### **INTELLECTUAL PROPERTY**

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published.

The SNIA IP Review Process is still in progress and is completing on xx/xx/xxxx. If IP disclosures that affect this specification are made during this process, this specification may be withdrawn.

Additional information can be found at the following locations:

• Results of IP Disclosures: <a href="https://www.snia.org/sffdisclosures">https://www.snia.org/sffdisclosures</a>

SNIA IP Policy: https://www.snia.org/corporate info/ippolicy

### **COPYRIGHT**

SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <a href="mailto:copyright\_request@snia.org">copyright\_request@snia.org</a>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

### **DISCLAIMER**

The information contained in this publication is subject to change without notice. SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to <a href="https://www.snia.org/feedback/">https://www.snia.org/feedback/</a>.

#### **FOREWORD**

The development work on this specification was done by the PCI-SIG, an industry group and given to the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, as well as since SFF's transition to SNIA in 2016, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TA TWG, the signup for membership can be found at <a href="https://www.snia.org/join">https://www.snia.org/join</a>.

### **REVISION HISTORY**

Rev 0.0.1 - March 28, 2025 Initial release

Rev 0.0.2 - May 1, 2025 2nd release incorporating comments informally Incorporating comments from the 1st SFF ballot.

| 1              |                        | CONTENTS                                                           |    |

|----------------|------------------------|--------------------------------------------------------------------|----|

| 2              | 1. SCOI                | PE                                                                 | 6  |

| 3              | 2. REFE                | ERENCES AND CONVENTIONS                                            | 6  |

| 4              | 2.1 IN                 | IDUSTRY DOCUMENTS                                                  | 6  |

| 5              | 2.2 Sc                 | DURCES                                                             | 7  |

| 6              | 2.3 Cd                 | ONVENTIONS                                                         | 8  |

| 7              | 3. KEYV                | WORDS, ACRONYMS, AND DEFINITIONS                                   | 9  |

| 8              | 3.1 KE                 | EYWORDS                                                            | 9  |

| 9              |                        | CRONYMS AND ABBREVIATIONS                                          |    |

| 10             |                        | EFINITIONS                                                         |    |

| 11             |                        | ERAL DESCRIPTION                                                   |    |

|                |                        | Onfiguration Overview/Descriptions                                 |    |

| 12<br>13       |                        | ONFIGURATION OVERVIEW/ DESCRIPTIONS                                |    |

|                |                        |                                                                    |    |

| <b>L4</b>      | 5. COM                 | IPLIANCE BOARDS AND REFERENCE POINTS FOR ACTIVE MODULES            | 15 |

| 15             | 6. ELEC                | CTRICAL SPECIFICATION                                              | 17 |

| 16             | 6.1 EL                 | ECTRICAL CONNECTOR                                                 | 17 |

| L7             | 6.1.1                  | x4 Connector and Pad Definition                                    | 17 |

| 18             | 6.1.2                  | PCIe x4 Example Circuits                                           | 19 |

| L9             | 6.1.3                  | X8 Connector and Pad Definition                                    | 20 |

| 20             | 6.1.4                  | PCIe x8 Example Circuits                                           |    |

| 21             | 6.1.5                  | x16 Connector and Pad Definition                                   | 23 |

| 22             | 6.1.6                  | PCIe x16 Example Circuits                                          | 27 |

| 23             | _                      | EXIOS                                                              | _  |

| 24             |                        | DW SPEED SIGNAL DESCRIPTIONS                                       |    |

| 25             | 6.3.1                  | LowPwrRequestHW                                                    |    |

| 26             | 6.3.2                  | IntLs                                                              |    |

| 27             | 6.3.3                  | PRPE                                                               |    |

| 28             | 6.3.4                  | PERST#                                                             | _  |

| 29             | 6.3.5                  | ResetLs                                                            |    |

| 30             | 6.3.6                  | SCL/SDA                                                            |    |

| 31<br>32       | 6.3.7                  | Pass-Through 2WCL/2WDA                                             |    |

| 33             | 6.4 Lc<br><i>6.4.1</i> | DW SPEED SIGNAL ELECTRICAL SPECIFICATIONS                          |    |

| 33<br>34       |                        | LOW Speed Signating                                                |    |

| 35             | 6.5.1                  | Management Interface Timing Specification                          |    |

| 36             | 6.5.2                  | TWI(I2C) Bus Pull Up Resistor                                      |    |

| 37             | 6.5.3                  | Timing for soft control and status functions                       |    |

| 38             |                        | IGH SPEED ELECTRICAL SPECIFICATION                                 |    |

| 39             | 6.6.1                  | Receive PER(n)(p/n)                                                |    |

| 10             | 6.6.2                  | Transmit PET(n)(p/n)                                               |    |

| 11             | <i>6.7</i> Pc          | OWER REQUIREMENTS                                                  | 39 |

| 12             | 6.7.1                  | Power Classes and Maximum Power Consumption                        | 39 |

| <del>1</del> 3 | 6.7.2                  | Host Board Power Supply Filtering                                  | 40 |

| 14             | 6.7.3                  | Module Power Supply Specification                                  | 40 |

| <del>1</del> 5 | 6.7.4                  | Host and Module Output Noise                                       |    |

| 16             | 6.7.5                  | Host Board Power Supply Noise Output                               |    |

| 17             | 6.7.6                  | Module Power Supply Noise Output                                   |    |

| 18             | 6.7.7                  | Module Power Supply Noise Tolerance                                |    |

| 19             | 6.7.8                  | Module Power Supply Noise Tolerance with Commercial Injector Probe | 46 |

| 1      | 6.8           | Clocking Considerations                                                                  | 48 |

|--------|---------------|------------------------------------------------------------------------------------------|----|

| 2      | 6.8.1         | Data Path Description                                                                    | 48 |

| 3      | 6.8.2         | Tx Clocking Considerations                                                               | 48 |

| 4      | 6.8.3         | Rx Clocking Considerations                                                               | 48 |

| 5      | 6.9           | ESD                                                                                      | 48 |

| 6      |               |                                                                                          |    |

| 7<br>8 | FIGURES       |                                                                                          |    |

| 9      |               | PLUG AND RECEPTACLE DEFINITION                                                           | 11 |

| 10     |               | WIPE FOR A CONTINUOUS CONTACT                                                            |    |

| 11     |               | : APPLICATION REFERENCE MODEL                                                            |    |

| 12     |               | REFERENCE POINTS AND COMPLIANCE BOARDS                                                   |    |

| 13     |               | PCIE OPTILINK X4 MODULE/CABLE PADS                                                       |    |

| 14     |               | PCIE X4 APPLICATION REFERENCE MODEL                                                      |    |

| 15     |               | PCIE AT AFFEICATION NET ERENCE MODEL  PCIE OPTILINK x8 MODULE/CABLE PADS                 |    |

| 16     |               | PCIE X8 APPLICATION REFERENCE MODEL                                                      |    |

| 17     |               | PCIE AS AFFEICATION NET ERENCE MODEL  PCIE OPTILINK x16 MODULE/CABLE PADS                |    |

| 18     |               | PCIE X16 APPLICATION REFERENCE MODEL                                                     |    |

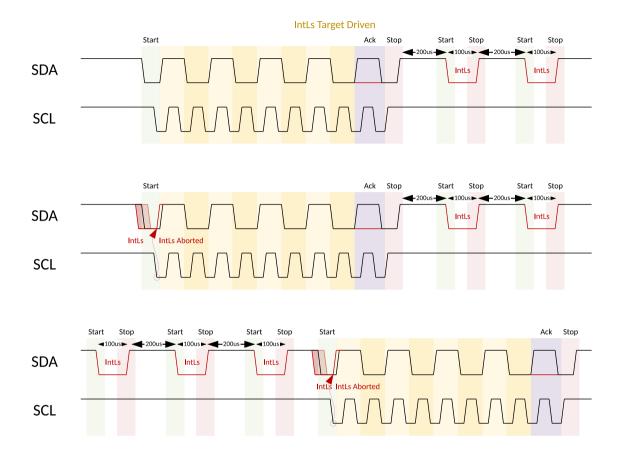

| 19     |               | INTLS OPERATION                                                                          |    |

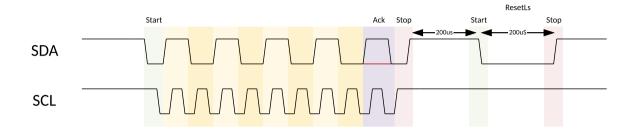

| 20     |               | RESTLS OPERATION                                                                         | _  |

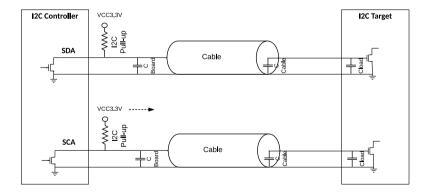

| 21     |               | : ARCHITECTURE OF PASS-THROUGH TWI                                                       |    |

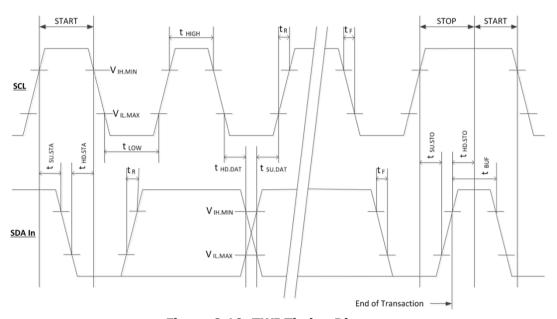

| 22     |               | D: TWI TIMING DIAGRAM                                                                    |    |

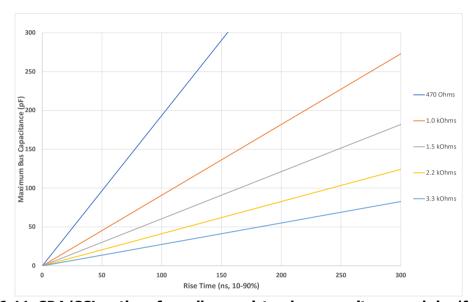

| 23     |               | 1: SDA/SCL OPTIONS FOR PULL-UP RESISTOR, BUS CAPACITANCE AND RISE/FALL TIMES             |    |

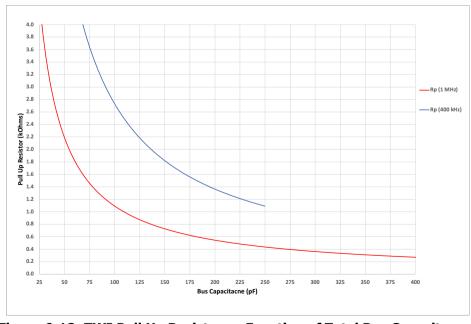

| 24     |               | 2: TWI PULL UP RESISTOR AS FUNCTION OF TOTAL BUS CAPACITANCE                             |    |

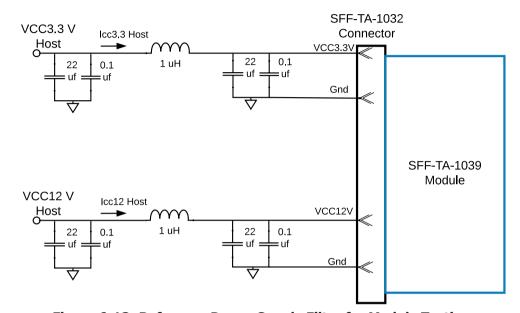

| 25     |               | 3: REFERENCE POWER SUPPLY FILTER FOR MODULE TESTING                                      |    |

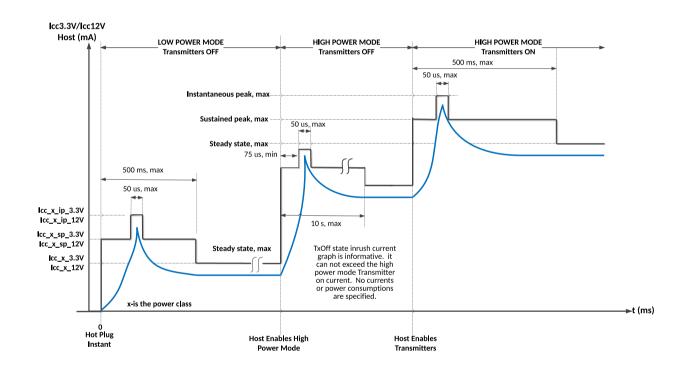

| 26     |               | 4: INSTANTANEOUS AND SUSTAINED PEAK CURRENTS FOR ICC3.3V/ICC12V HOST (SEE TABLE 6-10)    |    |

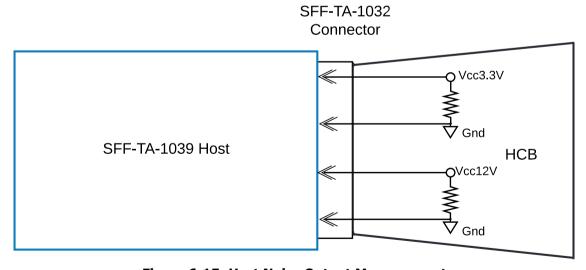

| 27     |               | 5: HOST NOISE OUTPUT MEASUREMENT                                                         |    |

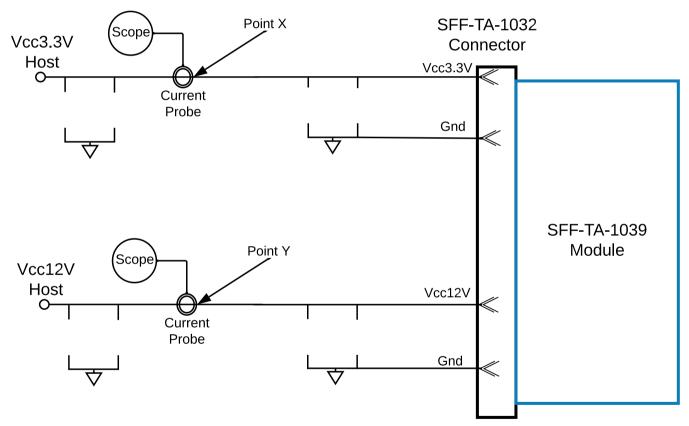

| 28     |               | 6: Module Noise Output Measurement                                                       |    |

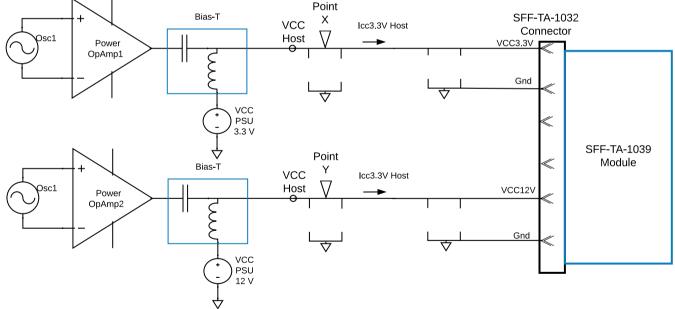

| 29     |               | 7: Module High Frequency Noise Tolerance                                                 |    |

| 30     |               | 8: Module Low Frequency Noise Tolerance                                                  |    |

| 31     |               | 9: Broadband Noise Tolerance Injection Probe Setup                                       |    |

| 32     | I IGORE O 1.  | J. DIOADBAND NOISE TOLLIANCE INJECTION THOSE SETOT                                       |    |

| 33     |               |                                                                                          |    |

| 34     | <b>TABLES</b> |                                                                                          |    |

| 35     | _             | EXAMPLE USES OF PCIE OPTILINK FORMFACTORS                                                | 13 |

| 36     |               | PCI SIDE-BAND COMPATIBILITY                                                              |    |

| 37     |               | COMPLIANCE TEST POINTS                                                                   |    |

| 38     | TABLE 6-1:    | PCIE OPTILINK x4 Module/Cable Pads Definition                                            | 18 |

| 39     |               | PCIE OPTILINK x8 MODULE/CABLE PADS DEFINITION                                            |    |

| 40     |               | PCIE OPTILINK x16 MODULE/CABLE PADS DEFINITION                                           |    |

| 41     |               | LOW SPEED CONTROL AND SENSE SIGNALS                                                      |    |

| 42     |               | Management Interface timing parameters                                                   |    |

| 43     |               | TIMING FOR PCIE OPTILINK SOFT CONTROL AND STATUS FUNCTIONS                               |    |

| 44     |               | I/O TIMING FOR SQUELCH & DISABLE                                                         |    |

| 45     |               | TX Squelch Levels                                                                        |    |

| 46     |               | Module Power Classes                                                                     |    |

| 47     |               | - Power supply specifications, instantaneous, sustained, and steady state current limits |    |

| 48     |               | - HOST AND MODULE OUTPUT NOISE AND TOLERANCE SPECIFICATIONS                              |    |

| 49     |               |                                                                                          |    |

#### 1. Scope 1

This specification defines electrical requirements for the 4x/8x/16x PCIe<sup>TM 1</sup> OptiLink modules and cables addressing compute and AI scale-up networks. The scope includes electrical contacts for the host connector; status, control and management interface signals; power supply requirements; and ESD.

4 5 6

7

8

2

3

High speed electrical specifications is based on PCI Express 64 GT/s [4] or 128 GT/s [6], and the connector pinout based on PCI Express CopprLink [3], and the multi-lane high speed mechanical specifications for 4x/8x/16x connector/cage specified by SFF-TA-1032 [7]. The 16x OptiLink connector/cage is similar to INF-TA-1003<sup>2</sup> [1], but only SFF-TA-1032 connector/cage is compatible with Optilink module.

9 10

11

12

25

# 2. References and Conventions

#### 2.1 **Industry Documents**

- 13 The following documents are relevant to this specification:

- 14 INF-TA-1003 400 Gb/s (16 x 25 Gb/s) Pluggable Transceiver, 2018

- IEEE Std 802.3-2022 clause 52 Figure 52-2 15 [2]

- [3] PCI Express CopprLink 1.0 External Cable Specification for PCI Express 5.0 and 6.0, April 2024 16

- 17 [4] PCI Express Base Specifications Revisions 6.3, January 2024

- 18 PCI Express Base Specifications Revisions 6.4, June 2025 [5]

- PCI Express Base Specifications Revisions 7.0, June 2025 19 [6]

- 20 [7] SFF-TA-1032 Multi-Lane External High Speed Cable System, Rev 1.0, March 2025

- 21 [8] SFF-8679 QSFP+ 4X Hardware and Electrical Specification, Rev 1.8.4, January 2025

- 22 [9] NXP UM10204, I2C-bus specification and user manual, Rev 7.0, October 2021

- 23 MIPI Alliance I3C Basic Specification, Rev 1.1.1, June 2021. [10]

- 24 [11] OIF Common Management Interface (CMIS), Rev. 5.3, September 2024

- https://www.oiforum.com/wp-content/uploads/OIF-CMIS-05.3.pdf

- 26 [12] OIF Common Electrical (I/O) (CEI), Rev. 5.2, January 2024 27

- https://www.oiforum.com/wp-content/uploads/OIF-CEI-05.2.pdf

- 28 [13] Formfactor Specific Hardware Management CMIS-FF, Rev. 1.0 September 2024 29 https://www.oiforum.com/wp-content/uploads/OIF-CMIS-FF-01.0.pdf

- 30 [14] JEDEC JESD8C.01 Interface Standard for Nominal 3.0/3.3 V Supply Digital Integrated Circuit (LVCMOS)

- [15] Human Body Model per ANSI/ESDA/JEDEC JS-001 31

- 32 [16] EN6100-4-2 (IEC immunity standard on ESD), criterion B test specifications

- 33 [17] "Measuring PSNR/PSRR/PSMR to meet QSFP/OSFP high-speed Requirements", Steve Sandler, Bob Tarasewicz, Pavel Zivny, Tony Ambrose, DesignCon 2023. 34

- 35 "Power Integrity Testing Requirements Introduce Extreme Interconnect Measures", Steve Sandler, Signal [18] Integrity Journal, February 2023 36 37

- https://www.signalintegrityjournal.com/articles/2981-power-integrity-testing-requirements-introduceextreme-interconnect-measures.

39 40

<sup>&</sup>lt;sup>1</sup> PCEe is registered trademarks of PCI-SIG.

<sup>&</sup>lt;sup>2</sup> Although 16x PCIe OptiLink connector/cage is similar to INF-TA-1003 the formfactors are not compatible.

# 3 4 5 6

1

#### 2.2 **Sources**

The complete list of SFF documents which have been published, are currently being worked on, or that have been expired by the SFF Committee can be found at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Suggestions for improvement of this specification are welcome and should be submitted to https://www.snia.org/feedback.

Other standards may be obtained from the organizations listed below:

| Standard                                | Organization                                                             | Website                      |

|-----------------------------------------|--------------------------------------------------------------------------|------------------------------|

| ASME                                    | American Society of Mechanical Engineers (ASME)                          | https://www.asme.org         |

| Electronic Industries<br>Alliance (EIA) | Electronic Components Industry Association (ECIA)                        | https://www.ecianow.org      |

| IEEE                                    | Institute of Electrical and Electronics Engineers (IEEE)                 | https://www.ieee.org         |

| InfiniBand                              | InfiniBand Trade Association (IBTA)                                      | https://www.infinibandta.org |

| JEDEC                                   | Joint Electron Deice Engineering Council (JEDEC)                         | https://www.jedec.org        |

| OIF                                     | Optical Internetworking Forum (OIF)                                      | https://www.oiforum.com      |

| PCIe                                    | PCI-SIG                                                                  | https://pcisig.com           |

| SAS and other ANSI standards            | International Committee for Information<br>Technology Standards (INCITS) | https://www.incits.org       |

7 8

#### 2.3 **Conventions**

The following conventions are used throughout this document:

4 5 6

1 2

3

**DEFINITIONS:** Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

7

**ORDER OF PRECEDENCE:** If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

9 10 11

8

**LISTS:** Lists sequenced by lowercase or uppercase letters show no ordering relationship between the listed items.

12

EXAMPLE 1 - The following list shows no relationship between the named items:

13

a. red (i.e., one of the following colors):

14 15

A. crimson; or

16

B. pink;

17 18

b. blue; or c. green.

19 20

Lists sequenced by numbers show an ordering relationship between the listed items.

21

22

EXAMPLE 2 -The following list shows an ordered relationship between the named items:

23

1. top; 2. middle; and

24 25

3. bottom.

26 27 28

Lists are associated with an introductory paragraph or phrase and are numbered relative to that paragraph or phrase (i.e., all lists begin with an a. or 1. entry).

29 30 31

**DIMENSIONING CONVENTIONS:** The dimensioning conventions are described in ASME-Y14.5, Geometric Dimensioning and Tolerancing, All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

32 33 34

**NUMBERING CONVENTIONS:** The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

35 36 37

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

# 1 3. Keywords, Acronyms, and Definitions

2 For the purposes of this document, the following keywords, acronyms, and definitions apply.

## 3.1 Keywords

**May:** Indicates flexibility of choice with no implied preference.

May or may not: Indicates flexibility of choice with no implied preference.

**Obsolete:** Indicates that an item was defined in prior specifications but has been removed from this specification.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be implemented as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Prohibited:** Describes a feature, function, or coded value that is defined in a referenced specification to which this SFF specification makes a reference, where the use of said feature, function, or coded value is not allowed for implementations of this specification.

**Reserved:** Where the term is used for a signal on a connector contact, the function is set aside for future standardization. It is not available for vendor specific use. Where this term is used for bits, bytes, fields, and code values; the bits, bytes, fields, and code values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Restricted:** Refers to features, bits, bytes, words, and fields that are set aside for other standardization purposes. If the context of the specification applies to the restricted designation, then the restricted bit, byte, word, or field shall be treated as a value whose definition is not in scope of this document, and is not interpreted by this specification.

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

### 3.2 Acronyms and Abbreviations

- Active Copper Cable, a cable assembly with driver and analog equalizer

Active Electrical Cable, a cable assembly with repeater/retimer on both end

- **ANSI:** American National Standards Institute

- **AOC:** Active Optical Cable

- **ASIC:** Application specific integrated circuit

- **CDR:** Clock and data recovery 45 **CML:** Current mode logic

- 45 CML: Current mode logic

- **DC:** Direct current

- **EIA:** Electronic Industries Alliance 48 **EMI:** Electromagnetic interference

- **EMLB:** Early Mate Late Break 50 **ESD**: Electrostatic discharge

- **FC:** Fibre Channel

1 FPP: Front Panel Pluggable 2 Gb/s: Gigabits per second 3 GBd: Gigabaud per second

4 GT/s Gigatransfer per second (same as GBd) 5 International Electrotechnical Commission IEC: 6 IEEE: Institute of Electrical and Electronics Engineers 7 International Organization for Standardization ISO: 8 ITU: **International Telecommunications Union**

9 I2C: A two-wire serial communication protocol using a serial data line (SDA) and a serial clock line (SCL) 10 I3C: An improved faster two-wire serial communication protocol using a serial data line (SDA) and a serial

clock line (SCL) 11

12 JEDEC: Joint Electron Device Engineering Council

13 **LVCMOS:** Low voltage complementary metal oxide semiconductor

Low voltage transistor-transistor logic 14 LVTTL:

15 MDI: Media dependent interface MPO: Multi-fiber Push Pull connector 16 Network Equipment Building System 17 **NEBS:**

Printed circuit board 18 PCB:

19 PCI: Peripheral Component Interconnect (legacy interface)

20 PCIe: Peripheral Component Interconnect Express (Modern interface based on high-speed SerDes)

21 PCB: Printed circuit board

22 Differentia [p/n] PCI Express Transmitter Lanes PET: 23 PER: Differential [p/n] PCI Express Receiver Lanes

24 **PERST#:** A discrete functional reset to the endpoint device as defined by the PCI Express Base specification. Bidirectional signal (PResence/PESTI) used to indicate the attachment of a cable assembly and a module 25 PRPE: 26

to a port.

27 Repeater: A high-speed CDR circuit that is not protocol aware and uses the recovered clock to retransmit the 28 incoming data

**Retimer:** A PCIe physical layer that include a CDR that is protocol aware

30 Receiver Transmitter (this document uses PER for consistency with PCI Express) RX:

31 SerDes: Serializer-Deserializer

TIA: 32 **Telecommunications Industry Association**

33 TX: Transmitter (this document uses PET for consistency with PCI Express)

Two Wire Interface such as I2C. 34 TWI:

### 3.3 Definitions

**Connector:** Each half of an interface that, when joined together, establishes electrical contact and mechanical retention between two components. In this specification, the term connector does not apply to any specific gender; it is used to describe the receptacle, the plug or the card edge, or the union of receptacle to plug or card edge. Other common terms include connector interface, mating interface, and separable interface.

**Contact mating sequence:** A term used to describe the order of electrical contact established/ terminated during mating/un-mating. Other terms include contact sequencing, contact positioning, mate first/break last, EMLB (early mate late break) staggered contacts, and long pin/short pin.

**Module:** In this specification, module may refer to a plug assembly at the end of a copper (electrical) cable (passive or active) or a loopback.

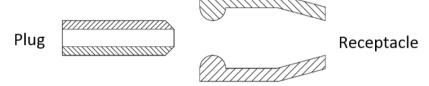

**Plug:** A term used to describe the connector that contains the penetrating contacts of the connector interface as shown in Figure 3-1. Plugs typically contain stationary contacts. Other common terms include male, pin connector, and card edge.

Figure 3-1 Plug and Receptacle Definition

**Receptacle:** A term used to describe the connector that contains the contacts that accept the plug contacts as shown in Figure 3-1. Receptacles typically contain spring contacts. Other common terms include female and socket connector.

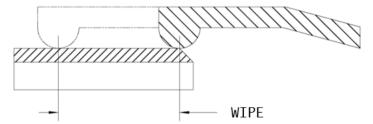

1 Wipe: The distance a contact travels on the surface of its mating contact during the mating cycle as shown in

2 Figure 3-2.

Figure 3-2 Wipe for a Continuous Contact

4 5

# 1 4. General Description

# 4.1 Configuration Overview/Descriptions

- 3 This specification covers the following items:

- Electrical specifications for 4x/8x/16x PCIe OptiLink (SFF-TA-1039) modules and cables including host connector contact assignments.

- Descriptions for data, control, status and management interface signals.

- Power supply requirements.

- Electrostatic discharge (ESD) tolerance requirements.

- Color coding and labeling.

- Fiber positions for optical interfaces.

- Environmental and thermal requirements (case temperatures).

- Timing requirements.

The high speed signaling for PCIe OptiLink module and cables are defined in PCI Express Gen 6.0 [4] and PCI Express Gen 7 [6], this specification expect to also be compatible with PCI Gen 5.0 if the connector is compatible with SFF-TA-1032 [7]. PCIe OptiLink modules and cables pinout are compatible with PCIe CopprLink [3]. Example modules and cables compatible with these specifications are listed in Table 4-1Error! Reference source not found.

18 19

20

2

4

5

6

7

8

9

10

11

12 13

14

15

16

17

**Table 4-1: Example uses of PCIe OptiLink Formfactors**

| 4x PCIe OptiLink  | PCI Express Gen 7.0 4x, PCI Express Gen 6.0 4x   |  |

|-------------------|--------------------------------------------------|--|

| 8x PCIe OptiLink  | PCI Express Gen 7.0 8x, PCI Express Gen 6.0 8x   |  |

| 16x PCIe OptiLink | PCI Express Gen 7.0 16x, PCI Express Gen 6.0 16x |  |

21 22

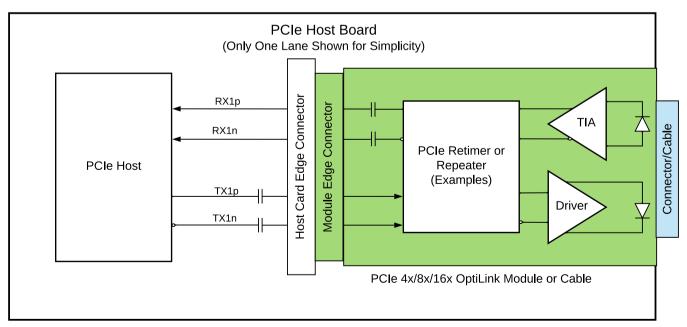

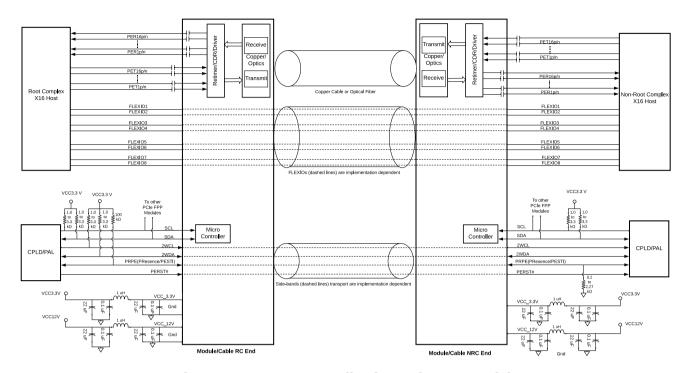

23 24 The Application Reference Model in Figure 4-1 shows the high-speed data interface between an PCIe Host and the module/cable. Only one lane of the interface is shown for simplicity. PCIe OptiLink implementation can be modules with parallel MPO connectors or cable assemblies with module attached (i.e., AOC, AEC, or ACC).

Figure 4-1: Application reference model

# 4.2 PCIe Compatibility

SFF-TA-1039 supports all of the CopprLink Side-band and FlexIOs, see Table 4-2. Order Sets (OS) have been in PCIe 64 GT/s [5] 128 GT/s [7], similar OS mechanisam maybe defined for SFF-TA-1039 side-bands but this is outside of the scope of this specifications.

**Table 4-2: PCI Side-band Compatibility**

| PCI Signals                                              | CopprLink / OptiLink<br>Side-band Signals | PCI Express Revision 6.4/7.0 Inband Signals using Order-sets |

|----------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------|

| PERST# (Reset end-point)                                 | Direct Wiring (x4, x8, x16)               | OS can be defined but may not meet NRC reset requirements    |

| PRPE (Presence/PESTI is Bi-Di Management)                | Direct Wiring (x4, x8, x16)               | Defined for CEM Presence but could be extended to cables     |

| 2WCL/2WDA (I2C for remote device management)             | Direct Wiring (x4, x8, x16)               | NA                                                           |

| FLEXIO1 (USB2p, PCIe x1 Txp, or GPIO TX or RX)           | Direct Wiring (x4, x8, x16)               | NA                                                           |

| FLEXIO2 (USB2n, PCIe x1 Txn, or GPIO TX or RX)           | Direct Wiring (x4, x8, x16)               | NA                                                           |

| FLEXIO3 (100 MHz REFCLK or PCIe x1 RXp GPIO TX or RX)    | Direct Wiring (x4, x8, x16)               | NA                                                           |

| FLEXIO4 (100 MHz REFCLK or PCIe x1 RXp or GPIO TX or RX) | Direct Wiring (x4, x8, x16)               | NA                                                           |

| FLEXIO5 (PCIe x1 RXp or GPIO TX or RX)                   | Direct Wiring (x16)                       | NA                                                           |

| FLEXIO6 (PCIe x1 RXp or GPIO TX or RX)                   | Direct Wiring (x16)                       | NA                                                           |

| FLEXIO7 (USB 2.0p or GPIO TX or RX)                      | Direct Wiring (x16)                       | NA                                                           |

| FLEXIO8 (USB 2.0n or GPIO TX or RX)                      | Direct Wiring (x16)                       | NA                                                           |

1 2

3

4

# 5. Compliance boards and reference points for active modules

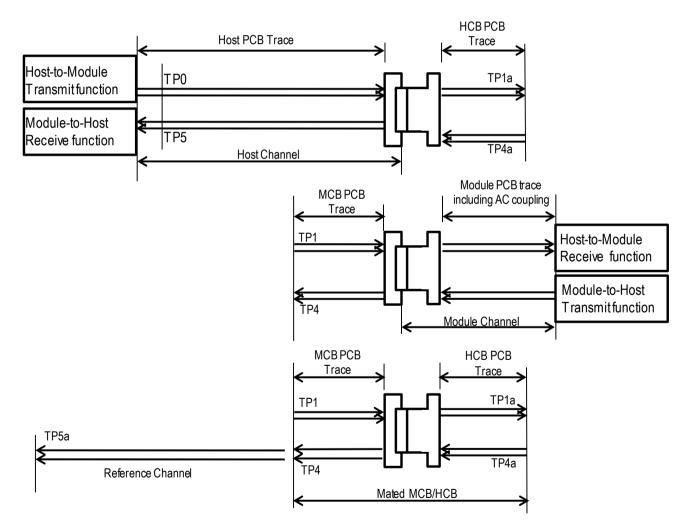

PCIe OptiLink uses MCB (Module Compliance Board) to measure AOC/AEC/ACC cable module end and uses HCB (Host Compliance Board) to measure the host. PCIe OptiLink modules and hosts electrical interfaces using compliance boards and test points as shown in Figure 5-1.

Reference test points are described in Table 5-1, PCIe OptiLink uses more complete test points consistent with SNIA SFF-8679 [8] and OIF CEI VSR [12] necessary for an active module. These compliance boards are intended to connect the module under test (DUT) to test equipment for verification of compliance to the appropriate standard. The electrical parameters of the compliance boards are specified by the appropriate standard.

Editor's note: There is an ongoing effort to define electrical compliance parameters for PCIe Optilink module in the PCI SIG.

The Module Compliance Board and Host Compliance Board can be plugged together for calibration of compliance signals and to check the electrical parameters of the compliance boards.

Figure 5-1: Reference Points and Compliance Boards

**Table 5-1: Compliance Test Points**

| Reference<br>Test<br>Points | Description                                                                                                                                                                          | Relationship to Current PCIe<br>Specifications                                                                                                                                             |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP0                         | Host ASIC transmitter output at ASIC package ball.                                                                                                                                   | Defined in the PCI Express Base as the ASIC ball.                                                                                                                                          |

| TP1                         | Input to Module Compliance Board. Used to test module input.                                                                                                                         | TP1 in this specification is identical to PCIe CopprLink test shown in Figure 4-1 and 4-2 Specifications [3] and PCIe Gen6/Gen7 Base Specifications [4]/[6]. Also used in the SFF-TA-1039. |

| TP1a                        | Host ASIC transmitter output through the host board and host card edge connector at the output of the Host Compliance Board. Also used to calibrate module input compliance signals. | Not currently defined by PCIe specifications but used in the SFF-TA-1039.                                                                                                                  |

| TP2 <sup>3</sup>            | Copper or optical medial dependent output MDI (not currently used by SFF-TA-1039), see                                                                                               | PCIe CopprLink [3] TP2 is equivalent to TP5a test point in this specification.                                                                                                             |

| TP3 <sup>4</sup>            | Copper or optical medial dependent input MDI (not currently used by SFF-TA-1039)                                                                                                     | Not used by PCIe Gen6/Gen7 Base Specifications [4]/[6].                                                                                                                                    |

| TP4                         | Input to Module Compliance Board. Used to test module output.                                                                                                                        | Defined by the PCIe CopprLink but is called TP2. Also used in the SFF-TA-1039.                                                                                                             |

| TP4a                        | Input to Host Compliance Board. Used to test host input.                                                                                                                             | Not currently defined by any PCIe specifications but used by the SFF-TA-1039.                                                                                                              |

| TP5                         | Input at the host ASIC ball.                                                                                                                                                         | TP5 in the PCI Express Base specifications is for replica channel input, which has no relationship to TP5 definition in this specification.                                                |

| TP5a                        | Far end module output through a reference channel.                                                                                                                                   | PCIe CopprLink [3] TP2 is equivalent to TP5a test point in this specification.                                                                                                             |

<sup>4</sup> 5 6

<sup>&</sup>lt;sup>3</sup> In this specification TP2 is reserved for potential future optical MDI output. TP2 definition in this specification is consistent with OIF definition and is not the same as TP2 definition in CopprLink, where CopprLink TP2 definition is the same as TP4 definition per this specification.

<sup>&</sup>lt;sup>4</sup> TP3 not used by PCI Express Base Specifications. In this specificationTP3 is reserved for potential future optical MDI output.

# 1 6. Electrical Specification

This chapter contains pad definition data for the module. The pad definition data is generic for high speed datacom applications such as PCI Express and Ethernet. Reference points for high-speed electrical measurements are defined in Table 5-1 and illustrated in Figure 5-1. Reference points for all other electrical signals are at comparable points at the host card edge connector.

### **6.1 Electrical Connector**

The module contains a printed circuit board that mates with the electrical connector. The pads are designed for a sequenced mating:

10 Connected first, disconnected last: - ground contacts

11 Connected second, disconnected second: - power contacts

12 Connected third, disconnected first: - signal contacts

For EMI protection the data signals to the connector should be shut off or held to a logic state when the module is absent. Standard board layout practices such as connections to Vcc and GND with vias, the use of short and equallength differential signal lines, and the use of strip-lines and 42.5  $\Omega$  terminations are recommended. The chassis ground (case common) of the module should be isolated from the module's circuit ground, GND, to provide the equipment designer flexibility regarding connections between external electromagnetic interference shields and circuit ground, GND, of the module.

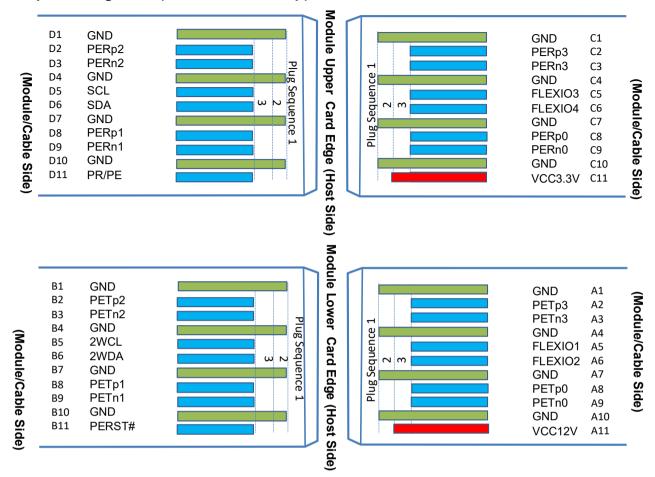

#### 6.1.1 x4 Connector and Pad Definition

Pad definition for the x4 connector is the same CopprLink x4 [3] but with additional details such as plug sequence and power to support active module. Figure 6-5 shows the signal symbols and pad numbering for the module edge connector. The diagram shows the module PCB edge as a top and bottom view, where bottom is nearer the host PCB. There are 44 pads intended for high-speed signals, low speed signals, power and ground connections. Color green identifies ground pads, color red identifies power pads, color orange identifies low speed signal/control pads, and color blue identifies high speed I/O pads. Table 6-1 provides more information about each of the 44 pads.

## Top Side Edge Card(viewed from the top)

Figure 6-1: PCIe OptiLink x4 Module/Cable Pads

4 5

6

1

2

3

Table 6-1: PCIe OptiLink x4 Module/Cable Pads Definition

| Pad | Logic                    | Symbol  | Description                                            | Plug<br>Sequence | Note |

|-----|--------------------------|---------|--------------------------------------------------------|------------------|------|

| A1  |                          | GND     | Ground                                                 | 1                | 1    |

| A2  | CML-I                    | PETp3   | Transmitter Non-Inverted Data Input                    | 3                |      |

| A3  | CML-I                    | PETn3   | Transmitter Inverted Data Input                        | 3                |      |

| A4  |                          | GND     | Ground                                                 | 1                | 1    |

| A5  | CML-I/O or<br>LVCMOS-I/O | FLEXIO1 | FlexIO use case: USB2p or PCIe x1 TXp<br>GPIO TX or RX | 3                |      |

| A6  | CML-I/O or<br>LVCMOS-I/O | FLEXIO2 | FlexIO use case: USB2n or PCIe x1 TXn GPIO TX or RX    | 3                |      |

| A7  |                          | GND     | Ground                                                 | 1                | 1    |

| A8  | CML-I                    | PETp0   | Transmitter Non-Inverted Data Input                    | 3                |      |

| A9  | CML-I                    | PETn0   | Transmitter Inverted Data Input                        | 3                |      |

| A10 |                          | GND     | Ground                                                 | 1                | 1    |

| A11 |                          | VCC12V  | VCC +12.0 V Power supply                               | 2                | 2    |

| B1  |            | GND     | Ground                                          | 1 | 1 |

|-----|------------|---------|-------------------------------------------------|---|---|

| B2  | CML-I      | PETp2   | Transmitter Non-Inverted Data Input             | 3 |   |

| В3  | CML-I      | PETn2   | Transmitter Inverted Data Input                 | 3 |   |

| B4  |            | GND     | Ground                                          | 1 | 1 |

| B5  | LVCMOS-I   | 2WCL    | Remote two-wire interface management bus clock  | 3 |   |

| B6  | LVCMOS-I/O | 2WDA    | Remote Two-wire interface management bus data   | 3 |   |

| B7  |            | GND     | Ground                                          | 1 | 1 |

| B8  | CML-I      | PETp1   | Transmitter Non-Inverted Data Input             | 3 |   |

| B9  | CML-I      | PETn1   | Transmitter Inverted Data Input                 | 3 |   |

| B10 |            | GND     | Ground                                          | 1 | 1 |

| B11 | LVCMOS-I/O | PERST#  | Through connected to reset the end point device | 3 | 3 |

| C1  |            | GND     | Ground                                          | 1 | 1 |

| C2  | CML-O      | PERp3   | Receiver Non-Inverted Data Input                | 3 |   |

| C3  | CML-O      | PERn3   | Receiver Inverted Data Input                    | 3 |   |

| C4  |            | GND     | Ground                                          | 1 | 1 |

| C5  | CML-I/O or | FLEXIO3 | FlexIO use case: PCIe x1 RXp                    | 3 | 3 |

|     | LVCMOS-I/O |         | GPIO TX or RX                                   |   |   |

| C6  | CML-I/O or | FLEXIO4 | FlexIO use case: PCIe x1 RXn                    | 3 | 3 |

|     | LVCMOS-I/O |         | GPIO TX or RX                                   |   |   |

| C7  |            | GND     | Ground                                          | 1 | 1 |

| C8  | CML-O      | PERp0   | Receiver Non-Inverted Data Input                | 3 |   |

| C9  | CML-O      | PERn0   | Receiver Inverted Data Input                    | 3 |   |

| C10 |            | GND     | Ground                                          | 1 | 1 |

| C11 |            | VCC3.3V | VCC +3.3 V Power supply                         | 2 | 2 |

| D1  |            | GND     | Ground                                          | 1 | 1 |

| D2  | CML-O      | PERp2   | Receiver Non-Inverted Data Input                | 3 |   |

| D3  | CML-O      | PERn2   | Receiver Inverted Data Input                    | 3 |   |

| D4  |            | GND     | Ground                                          | 1 | 1 |

| D5  | LVCMOS-I   | SCL     | Local two-wire interface management bus clock   | 3 |   |

| D6  | LVCMOS-I/O | SDA     | Local Two-wire interface management bus data    | 3 |   |

| D7  |            | GND     | Ground                                          | 1 | 1 |

| D8  | CML-O      | PERp1   | Receiver Non-Inverted Data Input                | 3 |   |

| D9  | CML-O      | PERn1   | Receiver Inverted Data Input                    | 3 |   |

| D10 |            | GND     | Ground                                          | 1 | 1 |

| D11 | LVCMOS-I/O | PRPE    | Bidirectional signal (Presence/PESTI)           | 3 | 3 |

Note 1: GND is the symbol for signal and supply (power) common for the module. All are common within the module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. For PCIe x4, each connector GND contact is rated for a maximum current of 500 mA.

Note 2: VCC3.3V is applied 1<sup>st</sup> and module power classes 1 operate from VCC3.3V only. VCC12V is applied after VCC3.3V reaches steady state (see Figure 6-14) and before module transitioned out of ModuleLowPwr. VCC3.3V and VCC12V contacts each have a steady state current rating of 3000 mA.

Note 3: For detail of FLEXIO's, 2WSCL, 2WSDL, PRPE, and PERST# see [3].

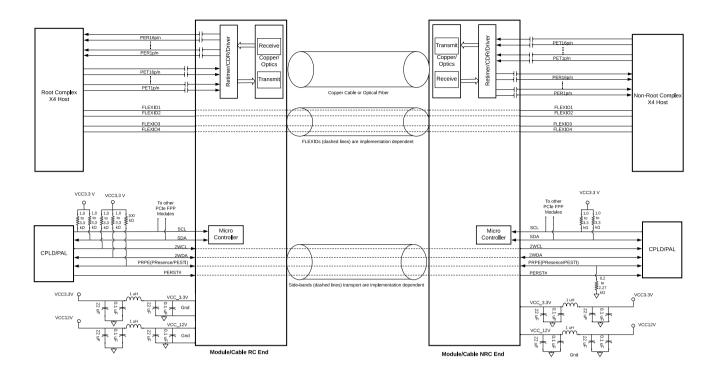

### 6.1.2 PCIe x4 Example Circuits

1

2

PCIe X4 OptiLink application reference model and example host RC and host NRC schematics are shown in Figure 6-2.

Figure 6-2: PCIe X4 Application Reference Model

#### 6.1.3 X8 Connector and Pad Definition

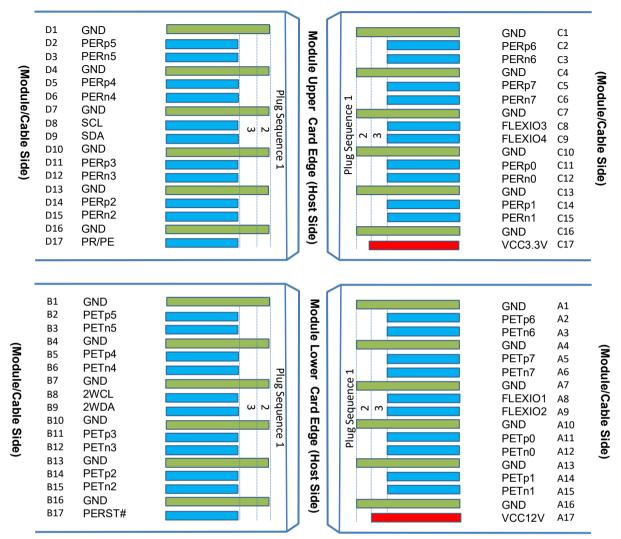

Pad definition for the x8 connector is the same CopprLink x8 [3] but with additional details such as plug sequence and power to support active module. Figure 6-3 shows the signal symbols and pad numbering for the module edge connector. The diagram shows the module PCB edge as a top and bottom view, where bottom is nearer the host PCB. There are 68 pads intended for high-speed signals, low speed signals, power and ground connections. Color green identifies ground pads, color red identifies power pads, color orange identifies low speed signal/control pads, and color blue identifies high speed I/O pads. Table 6-2 provides more information about each of the 68 pads.

# Top Side Edge Card(viewed from the top) Bottom Side Edge Card(viewed from the bottom)

Figure 6-3: PCIe OptiLink x8 Module/Cable Pads

Table 6-2: PCIe OptiLink x8 Module/Cable Pads Definition

| Pad | Logic                    | Symbol  | Description                                            | Plug<br>Sequence | Note |

|-----|--------------------------|---------|--------------------------------------------------------|------------------|------|

| A1  |                          | GND     | Ground                                                 | 1                | 1    |

| A2  | CML-I                    | PETp6   | Transmitter Non-Inverted Data Input                    | 3                |      |

| A3  | CML-I                    | PETn6   | Transmitter Inverted Data Input                        | 3                |      |

| A4  |                          | GND     | Ground                                                 | 1                | 1    |

| A5  | CML-I                    | PETp7   | Transmitter Non-Inverted Data Input                    | 3                |      |

| A6  | CML-I                    | PETn7   | Transmitter Inverted Data Input                        | 3                |      |

| A7  |                          | GND     | Ground                                                 | 1                | 1    |

| A8  | CML-I/O or<br>LVCMOS-I/O | FLEXIO1 | FlexIO use case: USB2p or PCIe x1 TXp<br>GPIO TX or RX | 3                |      |

| A9  | CML-I/O or<br>LVCMOS-I/O | FLEXIO2 | FlexIO use case: USB2n or PCIe x1 TXn<br>GPIO TX or RX | 3                |      |

| A10 |                          | GND     | Ground                                                 | 1                | 1    |

| A11 | CML-I                    | PETp0   | Transmitter Non-Inverted Data Input                    | 3                |      |

| A 1 2 | CML T      | DET:- C | The second the second of Date 1                 | 12 |   |

|-------|------------|---------|-------------------------------------------------|----|---|

| A12   | CML-I      | PETn0   | Transmitter Inverted Data Input                 | 3  | 1 |

| A13   | CNAL T     | GND     | Ground                                          | 1  | 1 |

| A14   | CML-I      | PETp1   | Transmitter Non-Inverted Data Input             | 3  |   |

| A15   | CML-I      | PETn1   | Transmitter Inverted Data Input                 | 3  | - |

| A16   |            | GND     | Ground                                          | 1  | 1 |

| A17   |            | VCC12V  | VCC +12.0 V Power supply                        | 2  | 1 |

| B1    | Chai T     | GND     | Ground                                          | 1  | 1 |

| B2    | CML-I      | PETp5   | Transmitter Non-Inverted Data Input             | 3  |   |

| B3    | CML-I      | PETn5   | Transmitter Inverted Data Input                 | 3  | 1 |

| B4    |            | GND     | Ground                                          | 1  | 1 |

| B5    | CML-I      | PETp4   | Transmitter Non-Inverted Data Input             | 3  |   |

| B6    | CML-I      | PETn4   | Transmitter Inverted Data Input                 | 3  |   |

| B7    |            | GND     | Ground                                          | 1  | 1 |

| B8    | LVCMOS-I   | 2WCL    | Remote two-wire interface management bus clock  | 3  | 3 |

| B9    | LVCMOS-I/O | 2WDA    | Remote Two-wire interface management bus data   | 3  | 3 |

| B10   |            | GND     | Ground                                          | 1  | 1 |

| B11   | CML-I      | PETp3   | Transmitter Non-Inverted Data Input             | 3  |   |

| B12   | CML-I      | PETn3   | Transmitter Inverted Data Input                 | 3  |   |

| B13   |            | GND     | Ground                                          | 1  | 1 |

| B14   | CML-I      | PETp2   | Transmitter Non-Inverted Data Input             | 3  | 3 |

| B15   | CML-I      | PETn2   | Transmitter Inverted Data Input                 | 3  | 3 |

| B16   |            | GND     | Ground                                          | 1  | 1 |

| B17   | LVCMOS-I/O | PERST#  | Through connected to reset the end point device | 3  | 3 |

| B17   | CML-I      | PETp7   | Transmitter Non-Inverted Data Input             | 3  |   |

| C1    |            | GND     | Ground                                          | 1  | 1 |

| C2    | CML-O      | PERp6   | Receiver Non-Inverted Data Input                | 3  |   |

| C3    | CML-O      | PERn6   | Receiver Inverted Data Input                    | 3  |   |

| C4    |            | GND     | Ground                                          | 1  | 1 |

| C5    | CML-O      | PERp7   | Receiver Non-Inverted Data Input                | 3  |   |

| C6    | CML-O      | PERn7   | Receiver Inverted Data Input                    | 3  |   |

| C7    |            | GND     | Ground                                          | 1  | 1 |

| C8    | CML-I/O or | FLEXIO3 | FlexIO use case: PCIe x1 RXp                    | 3  | 3 |

|       | LVCMOS-I/O |         | GPIO TX or RX                                   |    |   |

| C9    | CML-I/O or | FLEXIO4 | FlexIO use case: PCIe x1 RXn                    | 3  | 3 |

|       | LVCMOS-I/O |         | GPIO TX or RX                                   |    |   |

| C10   |            | GND     | Ground                                          | 1  | 1 |

| C11   | CML-O      | PERp0   | Receiver Non-Inverted Data Input                | 3  |   |

| C12   | CML-O      | PERn0   | Receiver Inverted Data Input                    | 3  |   |

| C13   |            | GND     | Ground                                          | 1  | 1 |

| C14   | CML-O      | PERp1   | Receiver Non-Inverted Data Input                | 3  | 3 |

| C15   | CML-O      | PERn1   | Receiver Inverted Data Input                    | 3  | 3 |

| C16   |            | GND     | Ground                                          | 1  | 1 |

| C17   |            | VCC3.3V | VCC +3.3 V Power supply                         | 2  | 2 |

| D1    |            | GND     | Ground                                          | 1  | 1 |

| D2    | CML-O      | PERp5   | Receiver Non-Inverted Data Input                | 3  |   |

| D3    | CML-O      | PERn5   | Receiver Inverted Data Input                    | 3  |   |

| D4    |            | GND     | Ground                                          | 1  | 1 |

| D5    | CML-O      | PERp4   | Receiver Non-Inverted Data Input                | 3  |   |

| D6    | CML-O      | PERn4   | Receiver Inverted Data Input                    | 3  |   |

| D7    |            | GND     | Ground                                          | 1  | 1 |

| D8    | LVCMOS-I   | 2WCL    | Remote two-wire interface management bus clock  | 3  |   |

| D9    | LVCMOS-I/O | 2WDA    | Remote Two-wire interface management bus data   | 3  |   |

|       |            |         | data                                            |    |   |

| D10 |            | GND   | Ground                                | 1 | 1 |

|-----|------------|-------|---------------------------------------|---|---|

| D11 | CML-O      | PERp3 | Receiver Non-Inverted Data Input      | 3 |   |

| D12 | CML-O      | PERn3 | Receiver Inverted Data Input          | 3 |   |

| D13 |            | GND   | Ground                                | 1 | 1 |

| D14 | CML-O      | PERp2 | Receiver Non-Inverted Data Input      | 3 |   |

| D15 | CML-O      | PERn2 | Receiver Inverted Data Input          | 3 |   |

| D16 |            | GND   | Ground                                | 1 | 1 |

| D17 | LVCMOS-I/O | PRPE  | Bidirectional signal (Presence/PESTI) | 3 | 3 |

Note 1: GND is the symbol for signal and supply (power) common for the module. All are common within the module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. For PCIe x8, each connector GND contact is rated for a maximum current of 500 mA.

Note 2: VCC3.3V is applied 1<sup>st</sup> and module power classes 1 operate from VCC3.3V only. VCC12V is applied after VCC3.3V reaches steady state (see Figure 6-14) and before module transitioned out of ModuleLowPwr. VCC3.3V and VCC12V contacts each have a steady state current rating of 3000 mA.

Note 3: For detail of FLEXIO's, 2WSCL, 2WSDL, PRPE, and PERST# see [3].

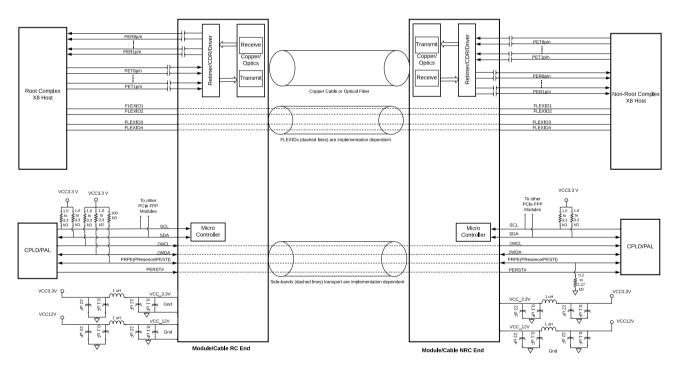

# **6.1.4 PCIe x8 Example Circuits**

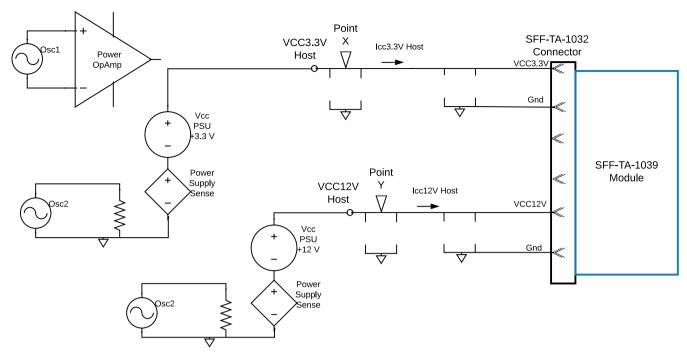

PCIe X4 OptiLink application reference model and example host RC and host NRC schematics are shown in Figure 6-4.

Figure 6-4: PCIe X8 Application Reference Model

#### 6.1.5 x16 Connector and Pad Definition

Pad definition for the x16 connector is the same CopprLink x16 [3] but with additional details such as plug sequence and power to support active module. Figure 6-5 shows the signal symbols and pad numbering for the module edge connector. The diagram shows the module PCB edge as a top and bottom view, where bottom is nearer the host PCB. There are 120 pads intended for high-speed signals, low speed signals, power and ground connections. Color green identifies ground pads, color red identifies power pads, color orange identifies low speed signal/control pads, and color blue identifies high speed I/O pads. Table 6-3 provides more information about each of the 120 pads.

5 6

7

8 9

10 11

12

13 14

1 2

3

#### D1 GND C1 GND D2 PERp11 PERp12 C2 PERn11 D3 PERn12 С3 D4 **GND GND** C4 PERp10 D5 PERp13 C5 D6 PERn10 PERn13 C6 D7 **GND C7** GND D8 PERp9 PERp14 C8 Module Upper Card D9 PERn9 PERn14 C9 D10 GND **GND** C10 PERp8 D11 PERp15 C11 D12 PERn8 PERn15 C12 (Module/Cable Side) Plug Sequence 1 D13 **GND** Sequence : **GND** C13 D14 FLEXIO7 FLEXIO5 C14 D15 FLEXIO8 3 2 FLEXIO6 C15 D16 GND GND C16 D17 PERp7 Edge (Host Side) PERp0 C17 D18 PERn7 PERn0 C18 D19 **GND** GND C19 D20 PERp6 PERp1 C20 D21 PERn6 PERn1 C21 D22 GND **GND** C22 D23 PERp5 PERp2 C23 D24 PERn5 PERn2 C24 **GND** D25 GND C25 D26 PERp4 C26 PERp3 D27 PERn4 PERn3 C27 D28 **GND GND** C28 D29 SCL VCC3.3V C29 D30 SDA PERST# C30 В1 GND **GND** Α1 В2 PETp11 PETp12 A2 PETn11 В3 PETn12 А3 **GND** В4 **GND** A4 **B5** PETp10 PETp13 Α5 В6 PETn10 PETn13 A6 В7 **GND GND** Α7 PETp9 В8 PETp14 Α8 Module Lower В9 PETn9 PETn14 Α9 B10 **GND GND** A10 B11 PETp8 PETp15 A11 B12 PETn8 PETn15 A12 (Module/Cable Side) Plug B13 **GND** Sequence **GND** A13 B14 FLEXIO3 Sequence 1 FLEXIO1 A14 Card Edge (Host Side B15 FLEXIO4 FLEXIO2 A15 B16 **GND** A16 **GND** B17 PETp7 PETp0 A17 B18 PETn7 PETn0 A18 B19 **GND GND** A19 Side) B20 PETp6 PETp1 A20 B21 PETn6 PETn1 A21 B22 GND A22 GND **B23** PETp5 PETp2 A23 PETn5 B24 PETn2 A24 B25 **GND GND** A25 B26 PETp4 PETp3 A26 B27 PETn4 PETn3 A27 B28 GND **GND** A28 VCC12V B29 2WCL A29 PR/PE B30 2WDL A30

Top Side Edge Card(viewed from the top) Bottom Side Edge Card(viewed from the bottom)

Figure 6-5: PCIe OptiLink x16 Module/Cable Pads

# Table 6-3: PCIe OptiLink x16 Module/Cable Pads Definition

| Pad | Logic                    | Plug<br>Sequence | Note                                                         |   |          |

|-----|--------------------------|------------------|--------------------------------------------------------------|---|----------|

| A1  |                          | GND              | Ground                                                       | 1 | 1        |

| A2  | CML-I                    | PETp12           | Transmitter Non-Inverted Data Input                          | 3 |          |

| A3  | CML-I                    | PETn12           | Transmitter Inverted Data Input                              | 3 |          |

| A4  |                          | GND              | Ground                                                       | 1 | 1        |

| A5  | CML-I                    | PETp13           | Transmitter Non-Inverted Data Input                          | 3 |          |

| A6  | CML-I                    | PETn13           | Transmitter Inverted Data Input                              | 3 |          |

| A7  |                          | GND              | Ground                                                       | 1 | 1        |

| A8  | CML-I                    | PETp14           | Transmitter Non-Inverted Data Input                          | 3 |          |

| A9  | CML-I                    | PETn14           | Transmitter Inverted Data Input                              | 3 |          |

| A10 |                          | GND              | Ground                                                       | 1 | 1        |

| A11 | CML-I                    | PETp15           | Transmitter Non-Inverted Data Input                          | 3 |          |

| A12 | CML-I                    | PETn15           | Transmitter Inverted Data Input                              | 3 |          |

| A13 |                          | GND              | Ground                                                       | 1 | 1        |

| A14 | CML-I/O or<br>LVCMOS-I/O | FLEXIO1          | FlexIO use case: USB2p or PCIe x1 TXp<br>GPIO TX or RX       | 3 |          |

| A15 | CML-I/O or<br>LVCMOS-I/O | FLEXIO2          | FlexIO use case: USB2n or PCIe x1 TXn<br>GPIO TX or RX       | 3 |          |

| A16 |                          | GND              | Ground                                                       | 1 | 1        |

| A17 | CML-I                    | PETp0            | Transmitter Non-Inverted Data Input                          | 3 | †        |

| A18 | CML-I                    | PETn0            | Transmitter Inverted Data Input                              | 3 |          |

| A19 |                          | GND              | Ground                                                       | 1 | 1        |

| A20 | CML-I                    | PETp1            | Transmitter Non-Inverted Data Input                          | 3 |          |

| A21 | CML-I                    | PETn1            | Transmitter Inverted Data Input                              | 3 |          |

| A22 |                          | GND              | Ground                                                       | 1 | 1        |

| A23 | CML-I                    | PETp2            | Transmitter Non-Inverted Data Input                          | 3 | <u> </u> |

| A24 | CML-I                    | PETn2            | Transmitter Inverted Data Input                              | 3 |          |

| A25 |                          | GND              | Ground                                                       | 1 | 1        |

| A26 | CML-I                    | PETp3            | Transmitter Non-Inverted Data Input                          | 3 | <u> </u> |

| A27 | CML-I                    | PETn3            | Transmitter Inverted Data Input                              | 3 |          |

| A28 |                          | GND              | Ground                                                       | 1 |          |

| A29 | LVCMOS-I                 | 2WCL             | Remote two-wire interface management bus clock               | 3 | 3        |

| A30 | LVCMOS-I/O               | 2WDA             | Remote Two-wire interface management bus data                | 3 | 3        |

| B1  | ,                        | GND              | Ground                                                       | 1 | 1        |

| B2  | CML-I                    | PETp11           | Transmitter Non-Inverted Data Input                          | 3 |          |

| В3  | CML-I                    | PETn11           | Transmitter Inverted Data Input                              | 3 |          |

| B4  |                          | GND              | Ground                                                       | 1 | 1        |

| B5  | CML-I                    | PETp10           | Transmitter Non-Inverted Data Input                          | 3 |          |

| B6  | CML-I                    | PETn10           | Transmitter Inverted Data Input                              | 3 |          |

| B7  |                          | GND              | Ground                                                       | 1 | 1        |

| B8  | CML-I                    | PETp9            | Transmitter Non-Inverted Data Input                          | 3 |          |

| В9  | CML-I                    | PETn9            | Transmitter Inverted Data Input                              | 3 |          |

| B10 |                          | GND              | Ground                                                       | 1 | 1        |

| B11 | CML-I                    | PETp8            | Transmitter Non-Inverted Data Input                          | 3 |          |

| B12 | CML-I                    | PETn8            | Transmitter Inverted Data Input                              | 3 |          |

| B13 |                          | GND              | Ground                                                       | 1 | 1        |

| B14 | CML-I/O or<br>LVCMOS-I/O | FLEXIO3          | FlexIO use case: 100 MHz REFCLK or PCIe x1 RXp GPIO TX or RX | 3 | 3        |

| B15 | CML-I/O or               | FLEXIO4          | FlexIO use case: 100 MHz REFCLK or PCIe x1 RXn               | 3 | 3        |

|     | LVCMOS-I/O   |          | GPIO TX or RX                                              |   |   |

|-----|--------------|----------|------------------------------------------------------------|---|---|

| B16 |              | GND      | Ground                                                     | 1 | 1 |

| B17 | CML-I        | PETp7    | Transmitter Non-Inverted Data Input                        | 3 | - |

| B17 | CML-I        | PETp7    | Transmitter Non-Inverted Data Input                        | 3 |   |

| B18 | CML-I        | PETn7    | Transmitter Inverted Data Input                            | 3 |   |

| B19 | CIVIL-1      | GND      | Ground                                                     | 1 | 1 |

| B20 | CML-I        | PETp6    | Transmitter Non-Inverted Data Input                        | 3 | 1 |

| B21 | CML-I        | PETP6    |                                                            | 3 |   |

|     | CIVIL-1      | GND      | Transmitter Inverted Data Input                            | 1 | 1 |

| B22 | CML-I        | PETp5    | Ground                                                     | 3 | 1 |

| B23 |              | -        | Transmitter Non-Inverted Data Input                        |   |   |

| B24 | CML-I        | PETn5    | Transmitter Inverted Data Input                            | 3 | 4 |

| B25 | CN II T      | GND      | Ground                                                     | 1 | 1 |

| V26 | CML-I        | PETp4    | Transmitter Non-Inverted Data Input                        | 3 |   |

| B27 | CML-I        | PETn4    | Transmitter Inverted Data Input                            | 3 |   |

| B28 |              | GND      | Ground                                                     | 1 | 1 |

| B29 |              | VCC12V   | VCC +12.0 V Power supply                                   | 2 | 2 |

| B30 | LVCMOS-I/O   | PRPE     | Bidirectional signal (Presence/PESTI)                      | 3 | 3 |

| C1  |              | GND      | Ground                                                     | 1 | 1 |

| C2  | CML-O        | PERp12   | Receiver Non-Inverted Data Input                           | 3 |   |

| C3  | CML-O        | PERn12   | Receiver Inverted Data Input                               | 3 |   |

| C4  |              | GND      | Ground                                                     | 1 | 1 |

| C5  | CML-O        | PERp13   | Receiver Non-Inverted Data Input                           | 3 |   |

| C6  | CML-O        | PERn13   | Receiver Inverted Data Input                               | 3 |   |

| C7  |              | GND      | Ground                                                     | 1 | 1 |

| C8  | CML-O        | PERp14   | Receiver Non-Inverted Data Input                           | 3 |   |

| C9  | CML-O        | PERn14   | Receiver Inverted Data Input                               | 3 |   |

| C10 |              | GND      | Ground                                                     | 1 | 1 |

| C11 | CML-O        | PERp15   | Receiver Non-Inverted Data Input                           | 3 |   |

| C12 | CML-O        | PERn15   | Receiver Inverted Data Input                               | 3 |   |

| C13 |              | GND      | Ground                                                     | 1 | 1 |

| C14 | CML-I/O or   | FLEXIO5  | FlexIO use case: PCIe x1 RXp                               | 3 | 3 |

| 01. | LVCMOS-I/O   | . 22,420 | GPIO TX or RX                                              |   |   |

| C15 | CML-I/O or   | FLEXIO6  | FlexIO use case: PCIe x1 RXn                               | 3 | 3 |

| 010 | LVCMOS-I/O   | . 22,420 | GPIO TX or RX                                              |   |   |

| C16 | 210.100 40   | GND      | Ground                                                     | 1 | 1 |

| C17 | CML-O        | PERp0    | Receiver Non-Inverted Data Input                           | 3 | 1 |

| C18 | CML-O        | PERn0    | Receiver Inverted Data Input                               | 3 |   |

| C19 | CITE         | GND      | Ground                                                     | 1 | 1 |

| C20 | CML-O        | PERp1    | Receiver Non-Inverted Data Input                           | 3 | 1 |

| C21 | CML-O        | PERn1    | Receiver Inverted Data Input                               | 3 |   |

| C21 | CITE-U       | GND      | Ground                                                     | 1 | 1 |

| C23 | CML-O        | PERp2    | Receiver Non-Inverted Data Input                           | 3 | T |

|     | CML-O        |          | Receiver Inverted Data Input  Receiver Inverted Data Input | 3 |   |

| C24 | CITIL-U      | PERn2    |                                                            |   | 1 |

| C25 | CMLO         | GND      | Ground                                                     | 1 | 1 |

| C26 | CML-O        | PERp3    | Receiver Non-Inverted Data Input                           | 3 |   |

| C27 | CML-O        | PERn3    | Receiver Inverted Data Input                               | 3 |   |

| C28 |              | GND      | Ground                                                     | 1 | 1 |

| C29 | 11/01/05 7/5 | VCC3.3V  | VCC +3.3 V Power supply                                    | 2 | 2 |

| C30 | LVCMOS-I/O   | PERST#   | Through connected to reset the end point device            | 3 | 3 |

| D1  |              | GND      | Ground                                                     | 1 | 1 |

| D2  | CML-O        | PERp11   | Receiver Non-Inverted Data Input                           | 3 |   |

| D3  | CML-O        | PERn11   | Receiver Inverted Data Input                               | 3 |   |

| D4  |            | GND     | Ground                                        | 1 | 1 |

|-----|------------|---------|-----------------------------------------------|---|---|

| D5  | CML-O      | PERp10  | Receiver Non-Inverted Data Input              | 3 |   |

| D6  | CML-O      | PERn10  | Receiver Inverted Data Input                  | 3 |   |

| D7  |            | GND     | Ground                                        | 1 | 1 |

| D8  | CML-O      | PERp9   | Receiver Non-Inverted Data Input              | 3 |   |

| D9  | CML-O      | PERn9   | Receiver Inverted Data Input                  | 3 |   |

| D10 |            | GND     | Ground                                        | 1 | 1 |

| D11 | CML-O      | PERp8   | Receiver Non-Inverted Data Input              | 3 |   |

| D12 | CML-O      | PERn8   | Receiver Inverted Data Input                  | 3 |   |

| D13 |            | GND     | Ground                                        | 1 | 1 |

| D14 | CML-I/O or | FLEXIO7 | FlexIO use case: USB2p or                     | 3 | 3 |

|     | LVCMOS-I/O |         | GPIO TX or RX                                 |   |   |

| D15 | CML-I/O or | FLEXIO8 | FlexIO use case: USB2n or                     | 3 | 3 |

|     | LVCMOS-I/O |         | GPIO TX or RX                                 |   |   |

| D16 |            | GND     | Ground                                        | 1 | 1 |

| D17 | CML-O      | PERp7   | Receiver Non-Inverted Data Input              | 3 |   |

| D18 | CML-O      | PERn7   | Receiver Inverted Data Input                  | 3 |   |

| D19 |            | GND     | Ground                                        | 1 | 1 |

| D20 | CML-O      | PERp6   | Receiver Non-Inverted Data Input              | 3 |   |

| D21 | CML-O      | PERn6   | Receiver Inverted Data Input                  | 3 |   |

| D22 |            | GND     | Ground                                        | 1 | 1 |

| D23 | CML-O      | PERp5   | Receiver Non-Inverted Data Input              | 3 |   |

| D24 | CML-O      | PERn5   | Receiver Inverted Data Input                  | 3 |   |

| D25 |            | GND     | Ground                                        | 1 | 1 |

| D26 | CML-O      | PERp4   | Receiver Non-Inverted Data Input              | 3 |   |

| D27 | CML-O      | PERn4   | Receiver Inverted Data Input                  | 3 |   |

| D28 |            | GND     | Ground                                        | 1 | 1 |

| D29 | LVCMOS-I   | 2WCL    | Local two-wire interface management bus clock | 3 |   |

| D30 | LVCMOS-I/O | 2WDA    | Local Two-wire interface management bus data  | 3 |   |

Note 1: GND is the symbol for signal and supply (power) common for the module. All are common within the module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. For PCIe x16, each connector GND contact is rated for a maximum current of 500 mA.

Note 2: VCC3.3V is applied 1<sup>st</sup> and module power classes 1 operate from VCC3.3V only. VCC12V is applied after VCC3.3V reaches steady state (see Figure 6-14) and before module transitioned out of ModuleLowPwr. VCC3.3V and VCC12V contacts each have a steady state current rating of 3000 mA.

Note 3: For detail of FLEXIO's, 2WSCL, 2WSDL, PRPE, and PERST# see [3].

# 6.1.6 PCIe x16 Example Circuits

1

2

4

5