SNIA.®

# New Project Proposal

# ULP Gen7 PCIe Connector SFF-TA-1041

Olaotan Elenitoba-Johnson TE Connectivity 02/27/2025 Rev 4.0

## New Project Proposal: ULP Gen7 PCIe Connector

### Purpose of the new SFF project is to define a new PCIe Gen7 connector

- A new form factor offers the superior SI performance for PCIe Gen7 and addresses the need for low-profile application without sacrificing the board space

- SMT style receptacle with 850hm nominal impedance

- 2pcs connector cabling solution to remove the PCB paddle card from the assembly

- Consolidated 18DP of high-speed and 16 sidebands into one solution to support PCIe applications. The

intention is to support x8 but not limit the scope of this project to solely x8 applications.

## Editor: Olaotan Elenitoba-Johnson(TE Connectivity)

## Supporters:

- 1. TE Connectivity (Dan Gorenc)

- 2. Molex (Egide Murisa)

- 3. Juniper Networks (Jeffery Maki)

- 4. ACES (Mick Felton)

- 5. FIT (Alex An & Terry Little)

- 6. Nvidia (David Herring)

#### **Form Factor** Pitch 2.0mm pair to pair pitch Cable Plug Type **Right-Angled** Angled Exit Lateral Exit Straight Board Connector Type Vertical **Differential Pairs** x8 (18DP+16SB), x16 is under development Cable AWG Supported 29-34AWG **Electrical Specification** Target Speed PCIe Gen 7 and beyond Impedance 85Ω

3 | ©2022 Storage Networking Association. All Rights Reserved.

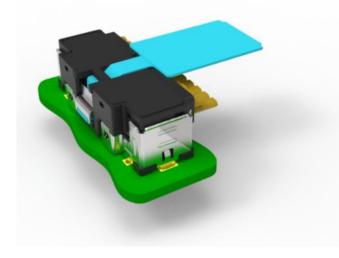

## **Overview of Connector Applications**

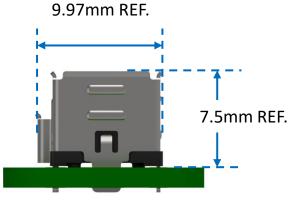

#### THE DIMENSIONS ARE SHOWN FOR RECEPTACLE ONLY

THE DIMENSIONS ARE SHOWN FOR MATING WITH RA CABLE PLUG

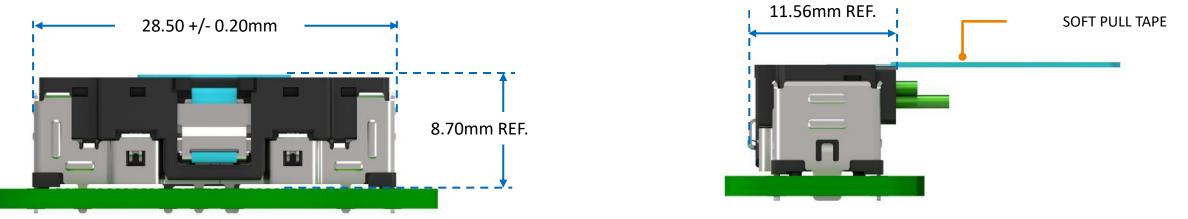

# Mating Height and Connector Outline Dimension Comparison between x8 SFF-TA-1016 and x8 ULP Gen7

ULP Gen7 addresses the need for ultra low-profile application without sacrificing the board space

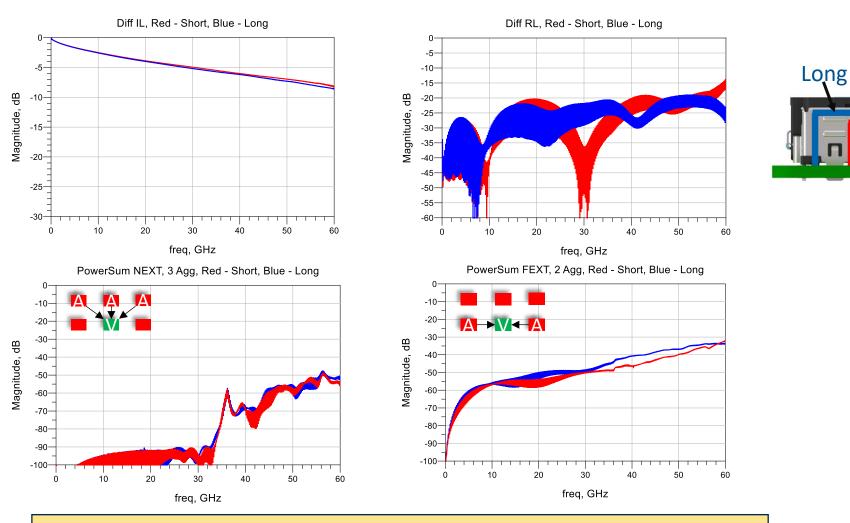

# TE PCIe 7.0 Mated Connector with Cable Termination SI

,**a**

**SNIA**

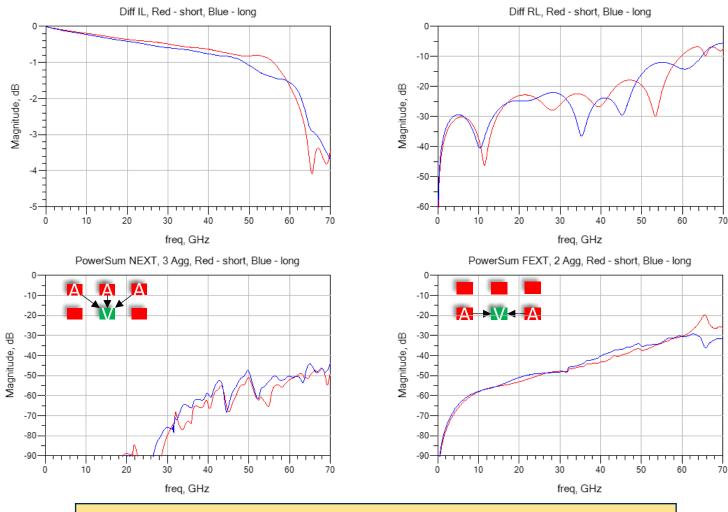

Model includes Host FP + VT Rcpt + RA Plug + Cable Term + 2mm of Bulk Cable

# TE PCIe 7.0 1meter 30AWG CA SI Simulation Results

Model includes Host FP + VT Rcpt + RA Plug + 1m 30AWG Bulk Cable + RA Plug + VT Rcpt + Host FP

,=

**SNIA**

7 | ©2022 Storage Networking Association. All Rights Reserved.

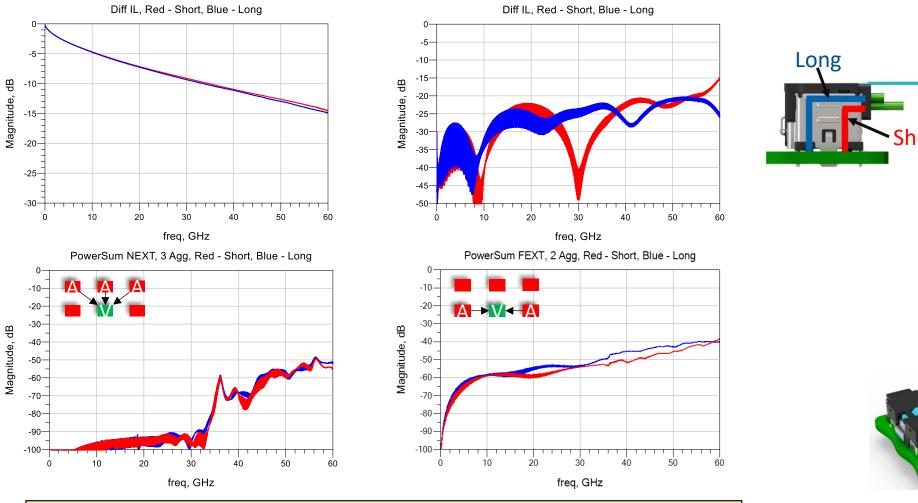

# TE PCIe 7.0 0.5meter 30AWG CA SI Simulation Results

Model includes Host FP + VT Rcpt + RA Plug + 0.5m 30AWG Bulk Cable + RA Plug + VT Rcpt + Host FP

,=

SNIA

8 | ©2022 Storage Networking Association. All Rights Reserved.

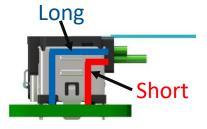

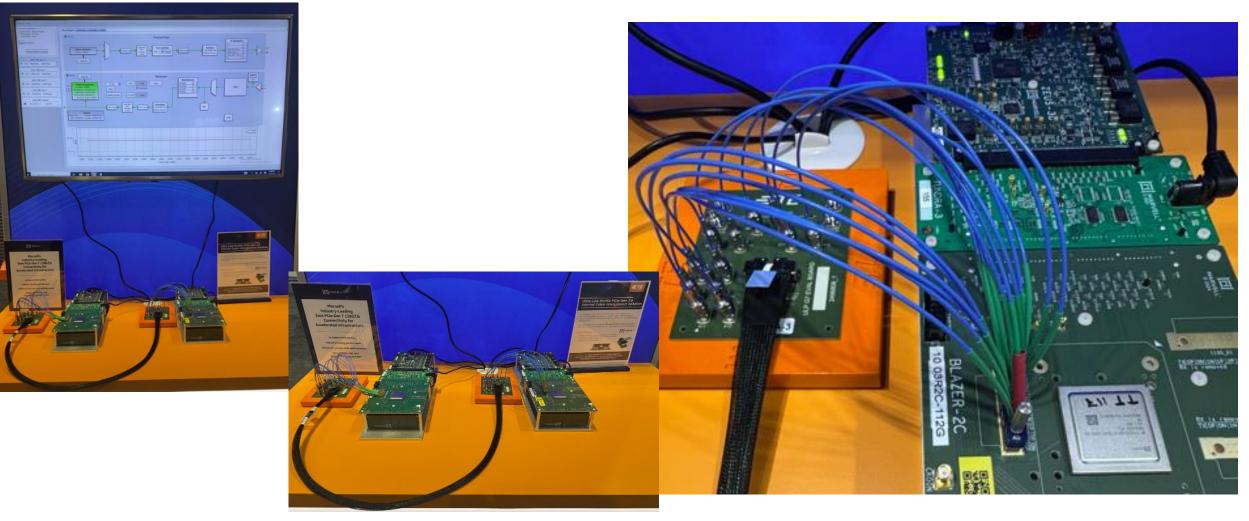

## Initial Prototypes Tooled, Tested & Demo'ed at DesignCon 2025

## Summary

- PCIe Gen 7 at 128Gtps justifies a fresh look at achieving performance objectives

- This project proposal enables an industry standard approach to address the higher data rate while also:

- Addresses the challenging thermal management environment on host design by providing lower profile mated solution (enhanced heat sink on host device above the interconnect)

- Smaller overall host envelope than existing solutions

- Superior signal integrity performance already demonstrated in first prototypes

- This project arms the industry with a standardized next gen internal cabled interconnect addressing needs not currently being met