# SFF-TA-1034

Specification for

# **Pluggable Multipurpose Module (PMM)**

Rev 1.0a

June 18, 2024

SECRETARIAT: SFF TA TWG

This specification is made available for public review at <u>https://www.snia.org/sff/specifications</u>. Comments may be submitted at <u>https://www.snia.org/feedback</u>. Comments received will be considered for inclusion in future revisions of this specification.

This specification provides a common reference for host systems manufacturers, host system integrators, and device suppliers.

The description of the details in this specification does not assure that the specific component is available from device suppliers. If such a device is supplied it shall comply with this specification to achieve interoperability between device suppliers.

ABSTRACT: This specification defines the mechanical attributes, pin list and pin placement, function of the pins, device specific electrical requirements, and specific features of a Pluggable Multipurpose Module for use in Enterprise and Datacenter systems. This specification relies on SFF-TA-1037 for the connector mechanicals.

POINTS OF CONTACT:

Anthony Constantine Intel Corporation 2111 NE 25th Ave, MS JF5-270 Hillsboro, OR 97124 Ph: 971 215 1128 Email: anthony.m.constantine@intel.com Anant Thakar Cisco Systems 170 West Tasman Dr. San Jose, CA 95134 Email: <u>athakar@cisco.com</u> Chairman SFF TA TWG Email: SFF-Chair@snia.org

#### Intellectual Property

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is considered SNIA Architecture and is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published. Additional information can be found at the following locations:

- Results of IP Disclosures: <u>https://www.snia.org/sffdisclosures</u>

- SNIA IP Policy: <u>https://www.snia.org/ippolicy</u>

#### Copyright

The SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <u>copyright request@snia.org</u>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

#### Disclaimer

The information contained in this publication is subject to change without notice. The SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to https://www.snia.org/feedback/.

#### Foreword

The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at <u>https://www.snia.org/sff/join</u>.

#### **Revision History**

- **Rev 1.0** *May 6, 2024:*

- Initial release.

- **Rev 1.0a** *May 13, 2024:*

- Added Figure 4-1 back (did not copy during publishing).

- Fixed PCIe BASE spec reference.

#### Contents

| 1. | Scope<br>1.1 Application Specific Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6<br>6                                                                                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2. | References and Conventions2.1Industry Documents2.2Sources2.3Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6<br>6<br>7                                                                                                |

| 3. | <ul> <li>Keywords, Acronyms, and Definitions</li> <li>3.1 Keywords</li> <li>3.2 Acronyms and Abbreviations</li> <li>3.3 Definitions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8<br>8<br>9                                                                                                |

| 4. | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                         |

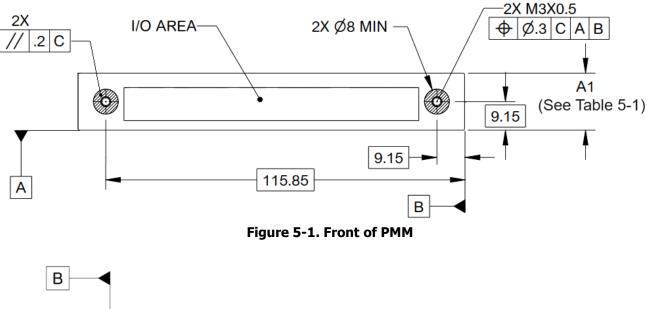

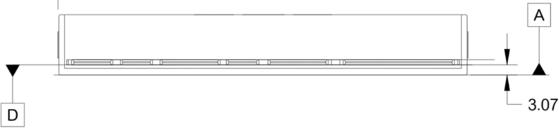

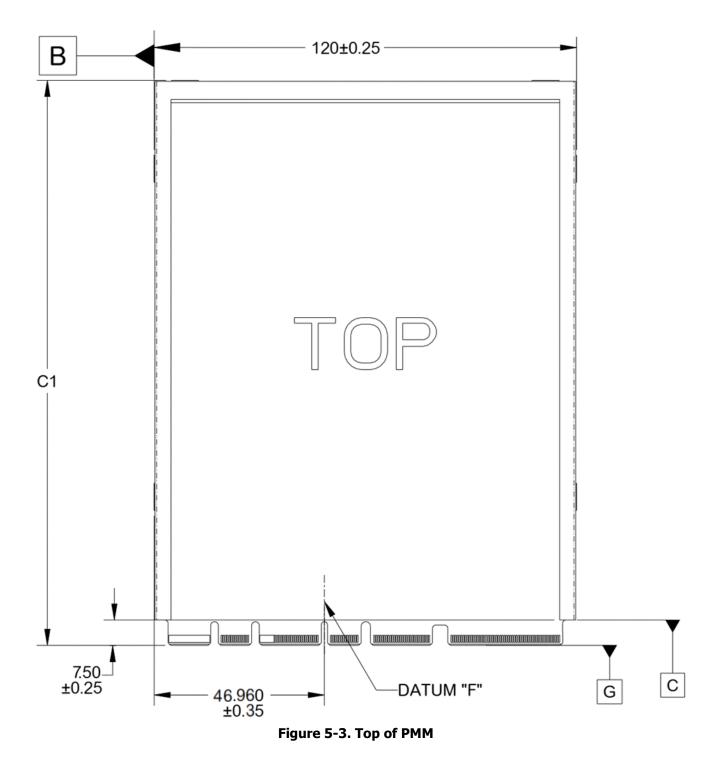

| 5. | Mechanical Specification<br>5.1 Overview<br>5.2 Physical Definition: PMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11<br>11<br>12                                                                                             |

| 6. | Signal List         6.1       Power and Grounds         6.2.       PCLE Signals         6.2.1       High Speed Signals (PERp/n, PETp/n)         6.2.2       Reference Clock (REFCLK[0.3][p/n])         6.2.3       PERST[07]#         6.2.4       Reference Clock Outputs (REFCLKOUT[p/n])         6.2.5       PERSTOUT#         6.3       Sideband Signals         6.3.1       PRSNT[03]#         6.3.2       PRSNTB[03]#         6.3.3       BRISTA#         6.3.4       GND/EDSFF_DETECT         6.3.5       BIF[02]#         6.3.6       AUX_PWR_EN         6.3.7       MAIN_PWR_EN         6.3.8       PMM_PWR_GOOD         6.3.9       PWRBRK#         6.3.10 RFU       6.4         6.4       M-PESTI         6.5       M-PESTI Interface         6.6.1       SMBus Interface         6.6.2       I3C Basic Output Interface         6.6.3       SMRST#         6.6.4       I3C Basic Output Interface         6.7.1       SGMII         6.8.1       USB_DATp, USB_DATn         6.9       Scan Chain         6.9.1       Scan Chain Interface | $\begin{array}{c} 15\\ 18\\ 18\\ 18\\ 19\\ 19\\ 19\\ 19\\ 20\\ 20\\ 20\\ 20\\ 20\\ 20\\ 20\\ 20\\ 20\\ 20$ |

| 7. | Electrical Requirements<br>7.1 Power Supply Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28<br>28                                                                                                   |

| <ul><li>7.2 Timings</li><li>7.3 3.3 V Logic Signal Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28<br>28                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

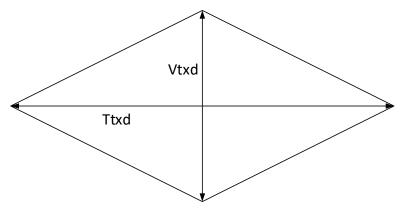

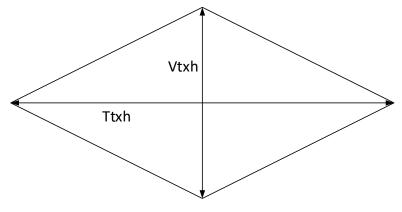

| <ol> <li>PCIe Electrical Requirements         <ol> <li>Signal Integrity Requirements</li> <li>Insertion Loss (IL)</li> <li>Return Loss (RL)</li> <li>Power Sum Near End Crosstalk (PSNEXT)</li> <li>Power Sum Far End Crosstalk (PSFEXT)</li> </ol> </li> <li>Transmitter and Receiver Sensitivity Eye Limits         <ol> <li>PMM Device Transmitter Eye Mask</li> <li>PMM Device Receiver Minimum Sensitivity</li> <li>PMM Host Receiver Minimum Sensitivity</li> </ol> </li> </ol>                                                                                                                                                                                                                                                                                             | 30<br>30<br>31<br>31<br>31<br>32<br>33<br>33<br>33<br>34<br>34<br>34                   |

| <ul> <li>9. Compatibility With Other Form Factors (Informative)</li> <li>9.1 OCP NIC 3.0</li> <li>9.1.1 Overview</li> <li>9.1.2 Mechanical Compatibility</li> <li>9.1.3 PCIe Electrical Compatibility</li> <li>9.1.4 Functional Compatibility</li> <li>9.2 EDSFF E3 (SFF-TA-1008)</li> <li>9.2.1 Overview</li> <li>9.2.2 Mechanical Considerations</li> <li>9.2.3 PCIe Electrical considerations</li> <li>9.2.4 Functional Compatibility</li> </ul>                                                                                                                                                                                                                                                                                                                               | 35<br>35<br>35<br>35<br>35<br>35<br>37<br>37<br>37<br>37<br>37<br>37                   |

| Figures<br>Figure 4-1. Example implementation of the Pluggable Multipurpose Module<br>Figure 5-1. Front of PMM<br>Figure 5-2. Back of PMM (card edge facing)<br>Figure 5-3. Top of PMM<br>Figure 5-4. Sides of PMM<br>Figure 6-1. PET and PER Signal Connectivity Between Host and Device<br>Figure 8-1. PMM Electrical Requirements Coverage<br>Figure 8-2. Example of Circuit Contributions to Insertion Loss and Return Loss<br>Figure 8-3. Example of PSNEXT Test Configuration for Device<br>Figure 8-4. Example of PSFEXT Victim and Aggressors<br>Figure 8-5. Eye Diagram for PMM Device Transmitter<br>Figure 8-6. Eye Diagram for PMM Host Transmitter<br>Figure 9-1. PMM Host Interposer for OCP NIC 3.0 Device<br>Figure 9-2. PMM Host Signal Changes for EDSFF Device | 10<br>12<br>12<br>13<br>14<br>18<br>30<br>31<br>32<br>32<br>32<br>33<br>34<br>36<br>38 |

| <b>Tables</b> Table 5-1. PMM DimensionsTable 6-1. PMM Connector Pin ListTable 6-2. REFCLK and PERST# Mapping Based on Bifurcation.Table 6-3. PMM Connector PinoutTable 7-1. Combined 12 V and HP_12V Power Supply RequirementsTable 7-2. 3.3 Vaux Power Supply RequirementsTable 7-3. DC Specification for 3.3 V Logic SignalingTable 8-1. Summary of Signal Integrity RequirementsTable 8-2. PMM Device Transmitter Eye Mask for PCIe at 32.0 GT/sTable 8-3. PMM Host Transmitter Eye Mask for PCIe at 32.0 GT/sTable 8-5. PMM Host Transmitter Eye Mask for PCIe at 64.0 GT/s                                                                                                                                                                                                   | 12<br>15<br>19<br>23<br>28<br>28<br>29<br>30<br>33<br>33<br>33<br>34<br>34             |

### Pluggable Multipurpose Module Specification

Page 5 Copyright  $\ensuremath{\mathbb{C}}$  2024 SNIA. All rights reserved.

# 1. Scope

The following specification defines the requirements for a device that is optimized for Enterprise and Datacenter applications.

# 1.1 Application Specific Criteria

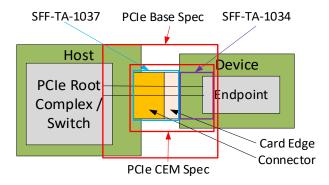

This specification defines the pin list and pin placement, function of the pins, device specific electrical requirements, and specific features of enterprise and datacenter-based devices. This specification relies on SFF-TA-1037 for the connector mechanicals.

# 2. References and Conventions

# 2.1 Industry Documents

The following documents are relevant to this specification:

- ASME Y14.5-2009 Dimensioning and Tolerancing published by ASME, available at https://www.asme.org.

- MIPI<sup>™</sup> Alliance Specification for I3C Basic, Version 1.0 available at https://www.mipi.org.

- Open Compute Project OCP NIC 3.0 Design Specification, revision 1.2.0 available at <a href="https://www.opencompute.org/wiki/Server/Mezz">https://www.opencompute.org/wiki/Server/Mezz</a>.

- PCI Express® (PCIe) Base Specification, revision 6.2, available from https://www.pcisig.com.

- PCI Express® (PCIe) Card Electromechanical Specification, revision 5.1, Version 1.0 available from <a href="https://www.pcisig.com">https://www.pcisig.com</a>.

- SNIA SFF-TA-1002 Card Edge multilane protocol agnostic connector specification available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- SNIA SFF-TA-1009 Enterprise and Datacenter Standard Form Factor Pin and Signal Specification <u>https://www.snia.org/sff/specifications</u>.

- SNIA SFF-TA-1037 Connectors for Pluggable Multi-Purpose Module available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- ENG-46158 Serial Gigabit Media Independent Interface (SGMII), Revision 1.8 available at <a href="https://ia803002.us.archive.org/25/items/sgmii/SGMII.pdf">https://ia803002.us.archive.org/25/items/sgmii/SGMII.pdf</a>

- System Management Bus (SMBus) Specification, Version 3.1, available from http://smbus.org.

- United Serial Bus (USB) Specification, Version 2.0, available from https://usb.org

# 2.2 Sources

The complete list of SFF documents which have been published, are currently being worked on, or that have been expired by the SFF Committee can be found at <u>https://www.snia.org/sff/specifications</u>. Suggestions for improvement of this specification are welcome and should be submitted to <u>https://www.snia.org/feedback</u>.

# 2.3 Conventions

The following conventions are used throughout this document:

**DEFINITIONS:** Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

**ORDER OF PRECEDENCE:** If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

**DIMENSIONING CONVENTIONS:** The dimensioning conventions are described in ASME-Y14.5, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

**NUMBERING CONVENTIONS:** The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

# 3. Keywords, Acronyms, and Definitions

For the purposes of this document, the following keywords, acronyms, and definitions apply.

# 3.1 Keywords

May or may not: Indicates flexibility of choice with no implied preference.

**Obsolete:** Indicates that an item was defined in prior specifications but has been removed from this specification.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be done in the same way as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Prohibited:** Describes a feature, function, or coded value that is defined in a referenced specification to which this SFF specification makes a reference, where the use of said feature, function, or coded value is not allowed for implementations of this specification.

**Reserved:** Defines the signal on a connector contact when its actual function is set aside for future standardization. It is not available for vendor specific use. Where this term is used for bits, bytes, fields, and code values; the bits, bytes, fields, and code values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Restricted:** Refers to features, bits, bytes, words, and fields that are set aside for other standardization purposes. If the context of the specification applies the restricted designation, then the restricted bit, byte, word, or field shall be treated as a reserved bit, byte, word, or field (e.g., a restricted byte uses the same value as defined for a reserved byte).

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

# 3.2 Acronyms and Abbreviations

PMM: Pluggable Multipurpose Module

# 3.3 Definitions

**Card:** Refers to the device plugged into a connector

**Contact Sequence:** The order that a device card edge pin makes physical contact to the host connector.

**Device:** Refers to the interface target.

**Dual Port:** When enabled, the device is configured with a PCIe port A and a PCIe port B. This is known as Dual Port mode. When disabled, all lanes form a single PCIe port A. In dual port mode, the two ports must operate independently. Any interaction between the two ports is outside the scope of the specification.

**Enclosure:** The housing that protects the internal components and acts as a heat sink.

**Endpoint:** The PCIe interface target logic located on the Device.

**Host:** Refers to the interface source or initiator.

**Root Complex:** The initiator source logic located on the Host.

**SRIS:** Acronym for Separate Reference clock Independent Spread spectrum clocking. This is a PCI Express feature that allows independent reference clocks for host and device. In this implementation, the host does not need to provide the reference clock and each independent source supports Spread Spectrum Clocking (SSC).

**SRNS:** Acronym for Separate Reference clock with No Spread spectrum clocking. This is a PCI Express feature that allows independent reference clocks for host and device. In this implementation, the host does not need to provide the reference clock and Spread Spectrum Clocking (SSC) is not enabled by either source.

**Switch:** A logic component located on the Host used to connect between a Root Complex and 1 or more Endpoints.

**Thickness:** Form factor dimension including PCB thickness, z-height of all components plus mechanicals.

# 4. General Description

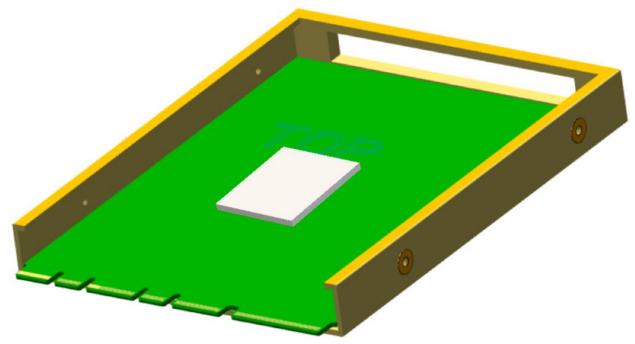

The application environment for the Pluggable Multipurpose Module (PMM) is a cabinet or enclosure connecting to one or more add-in cards. The device connects electrically to the system through a card edge connector as defined in SFF-TA-1037. This form factor is intended for use in enclosures that fit within a 1U or greater space (e.g., 1U refers to 1 standard unit of an IT equipment rack and the IT enclosures that fit in this space). An example of the form factor is shown in Figure 4-1. This specification defines the following features:

- PCIe support for existing and future specifications

- Supports 5.0 specification (up to 32.0 GT/s signaling).

- Supports 6.0 specification (up to 64.0 GT/s signaling).

- 1 card edge supporting up to 3 connectors as defined in SFF-TA-1037.

- A 168-pin receptacle supporting Sixteen (16) Tx and Rx PCIe lanes, up to 200W sustained for power, and sidebands (4C+).

- An optional power receptacle supporting up to an additional 400W sustained.

- An optional 108-pin receptacle supporting an additional Sixteen (16) Tx and Rx PCIe lanes.

- 2 device lengths supported:

- Short: 167 mm

- Long: 230 mm

- 2 device thicknesses supported:

- o 1/2U: 18.3 mm

- 1U: 38.4 mm

- Hot-plug capable connector and pin out but capability dependent on device support/usage.

- Common clock with options for SRIS and SRNS support by both host and device.

- Link Bifurcation control

- Support for sideband management over SMBus, I3C Basic, USB 2.0.

- Connector compatibility with SFF-TA-1008 and OCP NIC 3.0 (with host pin configurability or an interposer).

Figure 4-1. Example implementation of the Pluggable Multipurpose Module

# 5. Mechanical Specification

# 5.1 Overview

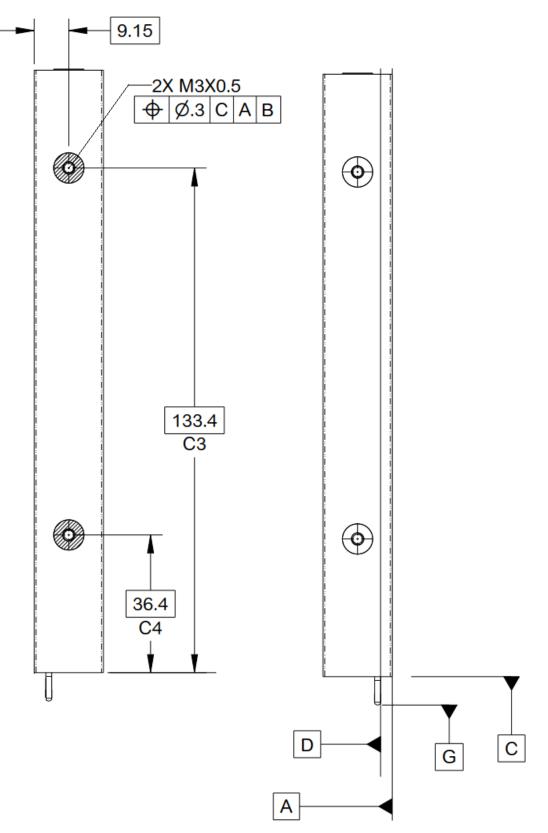

This section specifies the dimensions for the device form factor. The dimensioning convention is per ASME-Y14.5-2009 Dimensioning and Tolerancing. For mating interface details refer to SFF-TA-1037. This specification allows for device implementations that can vary in length and thickness. The following are nominal dimensions for four device variations:

- A 167 mm long x 120 mm wide x 18.30 mm thick form factor

- A 167 mm long x 120 mm wide x 38.40 mm thick form factor

- A 230 mm long x 120 mm wide x 18.30 mm thick form factor

- A 230 mm long x 120 mm wide x 38.40 mm thick form factor

No part of the host chassis of a host enclosure or parts connected to the mounting holes should encroach into any part of the bounding volume of the device form factor dimensions and tolerances as specified in this standard when the device is inserted into the host enclosure. The dimensioning convention is per ASME-Y14.5-2009 Dimensioning and Tolerancing.

The host should ensure the weight of the devices does not cause retention issues.

Unless specified, the default tolerance is +/- 0.15 mm. All dimensions provided in mm.

# 5.2 Physical Definition: PMM

| Dimensions | Millimeters | Tolerance | Comment                 |  |  |  |  |

|------------|-------------|-----------|-------------------------|--|--|--|--|

| A1a        | 18.30       | +0.2/-0.5 | Device Thickness (1/2U) |  |  |  |  |

| A1b        | 38.40       | +0.2/-0.5 | Device Thickness (1U)   |  |  |  |  |

| C1a        | 167         | 0.55      | Short device length     |  |  |  |  |

| C1b        | 230         | 0.55      | Long device length      |  |  |  |  |

Table 5-1. PMM Dimensions

Figure 5-2. Back of PMM (card edge facing)

Published

Figure 5-4. Sides of PMM

# 6. Signal List

This chapter covers the signal summary, definitions, and signal placement for the PMM connectors. Signal directions (I/O) are with respect to the host and the signals are mandatory for the device unless otherwise specified.

|           |                                  | Host |                                                                     |

|-----------|----------------------------------|------|---------------------------------------------------------------------|

| Interface | Signal Name                      | I/O  | Function                                                            |

|           | 12 V                             | 0    | +12 V power                                                         |

| Power and | HP_12 V                          | 0    | HP_12 V: High power +12 V power                                     |

| Grounds   | 3.3 Vaux                         | 0    | +3.3 V power                                                        |

|           | GND                              | 0    | Return current path                                                 |

|           | PETp0, PETn0                     | _    |                                                                     |

|           | PETp1, PETn1<br>PETp2, PETn2     | _    |                                                                     |

|           | PETp3, PETn3                     | _    |                                                                     |

|           | PETp4, PETn4                     | _    |                                                                     |

|           | PETp5, PETn5                     |      |                                                                     |

|           | PETp6, PETn6                     |      |                                                                     |

|           | PETp7, PETn7                     |      |                                                                     |

|           | PETp8, PETn8                     |      |                                                                     |

|           | PETp9, PETn9                     |      |                                                                     |

|           | PETp10, PETn10                   | _    |                                                                     |

|           | PETp11, PETn11                   | _    |                                                                     |

|           | PETp12, PETn12                   | _    |                                                                     |

|           | PETp13, PETn13                   | _    | PCIe TX Differential signals defined by the PCI                     |

|           | PETp14, PETn14<br>PETp15, PETn15 | _    | Express Card Electromechanical Specification.                       |

|           | PETp16, PETn16                   | - 0  | PETp/n[015] are supported with the x16 or x32                       |

|           | PETp17, PETn17                   | _    | connectors. PETp/n[1631] are supported only with                    |

|           | PETp18, PETn18                   |      | the x32 connector.                                                  |

|           | PETp19, PETn19                   | 1    |                                                                     |

| PCIe      | PETp20, PETn20                   |      |                                                                     |

|           | PETp21, PETn21                   |      |                                                                     |

|           | PETp22, PETn22                   | _    |                                                                     |

|           | PETp23, PETn23                   | _    |                                                                     |

|           | PETp24, PETn24                   |      |                                                                     |

|           | PETp25, PETn25<br>PETp26, PETn26 | _    |                                                                     |

|           | PETp27, PETn27                   | _    |                                                                     |

|           | PETp28, PETn28                   |      |                                                                     |

|           | PETp29, PETn29                   |      |                                                                     |

|           | PETp30, PETn30                   |      |                                                                     |

|           | PETp31, PETn31                   |      |                                                                     |

|           | PERp0, PERn0                     |      |                                                                     |

|           | PERp1, PERn1                     |      |                                                                     |

|           | PERp2, PERn2                     | _    | PCIe RX Differential signals defined by the PCI                     |

|           | PERp3, PERn3                     | ┥.   | Express Card Electromechanical Specification.                       |

|           | PERp4, PERn4                     | I    | PERp/n[015] are supported with the x16 or x32                       |

|           | PERp5, PERn5<br>PERp6, PERn6     |      | connectors. PERp/n[1631] are supported only with the x32 connector. |

|           | PERp7, PERn7                     |      |                                                                     |

|           | PERp8, PERn8                     | -    |                                                                     |

|           |                                  |      | I                                                                   |

#### Table 6-1. PMM Connector Pin List

Pluggable Multipurpose Module Specification

| Interface | Signal Name        | Host<br>I/O | Function                                                 |

|-----------|--------------------|-------------|----------------------------------------------------------|

|           | PERp9, PERn9       |             |                                                          |

|           | PERp10, PERn10     |             |                                                          |

|           | PERp11, PERn11     |             |                                                          |

|           | PERp12, PERn12     |             |                                                          |

|           | PERp13, PERn13     |             |                                                          |

|           | PERp14, PERn14     |             |                                                          |

|           | PERp15, PERn15     |             |                                                          |

|           | PERp16, PERn16     |             |                                                          |

|           | PERp17, PERn17     |             |                                                          |

|           | PERp18, PERn18     |             |                                                          |

|           |                    |             |                                                          |

|           | PERp19, PERn19     |             |                                                          |

|           | PERp20, PERn20     |             |                                                          |

|           | PERp21, PERn21     |             |                                                          |

|           | PERp22, PERn22     |             |                                                          |

|           | PERp23, PERn23     |             |                                                          |

|           | PERp24, PERn24     |             |                                                          |

|           | PERp25, PERn25     |             |                                                          |

|           | PERp26, PERn26     |             |                                                          |

|           | PERp27, PERn27     |             |                                                          |

|           | PERp28, PERn28     |             |                                                          |

|           | PERp29, PERn29     |             |                                                          |

|           | PERp30, PERn30     |             |                                                          |

|           | PERp31, PERn31     |             |                                                          |

|           | REFCLKp0, REFCLKn0 |             |                                                          |

|           | REFCLKp1, REFCLKn1 |             | PCIe Reference Clock signals defined by the PCI          |

|           | REFCLKp2, REFCLKn2 | 0           | Express Base Specification.                              |

|           | REFCLKp3, REFCLKn3 |             |                                                          |

|           | REFCLKOUTp0,       | -           |                                                          |

|           | REFCLKOUTn0        | I           | Reserved for Future Use                                  |

|           | PERST0#            |             |                                                          |

|           | PERST1#            |             |                                                          |

|           | PERST2#            |             |                                                          |

|           | PERST3#            |             | PE-Reset is a fundamental reset to the device defined    |

|           | PERST4#            | 0           | as PERST# by the <i>PCI Express Base Specification</i> . |

|           | PERST5#            |             |                                                          |

|           | PERST6#            | 1           |                                                          |

|           | PERST7#            |             |                                                          |

|           | PERSTOUT#          | I           | Reserved for Future Use                                  |

|           |                    | 1           | Active low signal. This signal indicates to the host     |

|           | PRSNTB0#           | Ι           | that the device is electrically attached.                |

|           |                    |             | Active low signal. This signal is used to detect device  |

|           | PRSNTB1#           | Ι           | presence.                                                |

|           |                    |             | Active low signal. This signal indicates to the host     |

| Sideband  | PRSNTB2#/ PRSNT0#  | Ι           | that the device is electrically attached.                |

| Signals   |                    |             | Active low signal. This signal is available in the x16   |

| Jigi lais |                    | I           |                                                          |

|           | PRSNTB3#/ PRSNT2#  |             | connector as a presence signal to indicate to the host   |

|           |                    |             | that the device is electrically attached.                |

|           | DDCNT2#            | т           | Active low signal. This signal is available in the x32   |

|           | PRSNT3#            | I           | connector as a presence signal to indicate to the host   |

|           |                    |             | that the device is electrically attached.                |

| Interface           | Signal Name           | Host<br>I/O | Function                                                                                                                                                                                                          |

|---------------------|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | LED                   | 0           | LED: Active high signal. This signal is used to drive<br>the amber or amber/blue LED state from the host to<br>the device. This signal is for EDSFF compatibility and<br>is not used by PMM.                      |

|                     | GND/EDSFF_DETECT      | Ι           | Active high signal. This signal indicates to the host that an EDSFF device is attached.                                                                                                                           |

|                     | BIF0#, BIF1#, BIF2#   | 0           | Active low signals. The bifurcation signals allow the host to configure the bifurcation support of the device as defined in the <i>OCP NIC 3.0 Design Specification</i> .                                         |

|                     | AUX_PWR_EN            | 0           | AUX_PWR_EN: Active high signal. Auxiliary power<br>enable is used to indicate the host is in aux power<br>mode as defined in the OCP NIC 3.0 Design<br>Specification.                                             |

|                     | MAIN_PWR_EN           | 0           | Active high signal. Main power enable is used to indicate the host is in main power mode as defined in the <i>OCP NIC 3.0 Design Specification</i> .                                                              |

|                     | PMM_PWR_GOOD          | Ι           | Active high signal. NIC power good is used to indicate that the device has good internal power in aux power mode and main power mode.                                                                             |

|                     | PWRBRK#               | 0           | Open drain active low signal with pull-up on device.<br>PWRBRK# communicates that an emergency power<br>reduction is needed as defined in the <i>PCI Express</i><br><i>Card Electromechanical Specification</i> . |

|                     | M-PESTI_IN            | 0           | Reserved for Future Use                                                                                                                                                                                           |

|                     | M-PESTI_OUT           | Ι           | Reserved for Future Use                                                                                                                                                                                           |

|                     | RFU                   |             | Reserved for Future Use                                                                                                                                                                                           |

|                     | SMBCLK/I3CCLK         | 0           | SMBCLK: Open Drain with pull-up on host. SMBus<br>Clock.<br>I3CCLK: Active high push-pull and open drain signal.<br>I3C Basic Clock.                                                                              |

| 2-wire<br>interface | SMBDATA/I3CDATA       | I/O         | SMBDATA: Open Drain with pull-up on host. SMBus<br>Data.<br>I3CDATA: Active high push-pull and open drain<br>signal. I3C Basic Data.                                                                              |

|                     | SMRST#                | 0           | Active low signal. SMRST# is a reset for the management interface.                                                                                                                                                |

|                     | SMBCLKOUT/I3CCLKOUT   | Ι           | I3CCLK: Active high push-pull and open drain signal.<br>I3C Basic Clock.                                                                                                                                          |

|                     | SMBDATAOUT/I3CDATAOUT | I/O         | I3CDATA: Active high push-pull and open drain signal. I3C Basic Data.                                                                                                                                             |

| 802.3<br>SGMII      | SGMII_TXp, SGMII_TXn  | 0           | Ethernet management port differential outputs as defined by <i>ENG-46158 Serial Gigabit Media Independent Interface.</i>                                                                                          |

| interface           | SGMII_RXp, SGMII_RXn  | I           | Ethernet management port differential inputs as defined by <i>ENG-46158 Serial Gigabit Media</i><br><i>Independent Interface.</i>                                                                                 |

|                     | USB_DATp, USB_DATn    | I/O         | USB interface as defined in the USB 2.0 Specification.                                                                                                                                                            |

| USB                 |                       |             |                                                                                                                                                                                                                   |

| USB                 | CLK                   | 0           | Active high signal. Scan Chain clock.                                                                                                                                                                             |

| USB<br>Scan Chain   | CLK<br>DATA_OUT       | 0           | Active high signal. Scan Chain clock.<br>Active high signal. Scan Chain data output signal.                                                                                                                       |

| Interface | Signal Name | Host<br>I/O | Function                                                  |  |

|-----------|-------------|-------------|-----------------------------------------------------------|--|

|           | LD#         | 0           | Active low signal. Scan Chain shift register load signal. |  |

# 6.1 **Power and Grounds**

The PMM connector supports a 12 V power source to power the device up to 200W. It also supports a 3.3 Vaux power source to provide power to manage sideband communication. All power and grounds shall be supported by the implemented connector on the host and the implemented card edge on the device.

The PMM connector also supports an optional high power 12 V power source called HP\_12 V that provides an additional 400W of power to the device.

There are no power sequencing requirements between 3.3 Vaux and 12 V/HP\_12 V. These voltages are independent from each other.

All devices are limited to 80W until the slot power limit support is set by the host. See the *PCI Express Base Specification* for more information.

# 6.2 PCIe Signals

# 6.2.1 High Speed Signals (PERp/n, PETp/n)

A device shall implement a minimum of one (1) PCIe lane. A lane consists of an input and output differential pair. Additional lanes are optional. Refer to the *PCI Express Base Specification* for more details on the functional requirements of the interface signals.

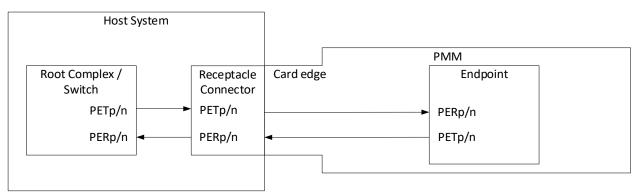

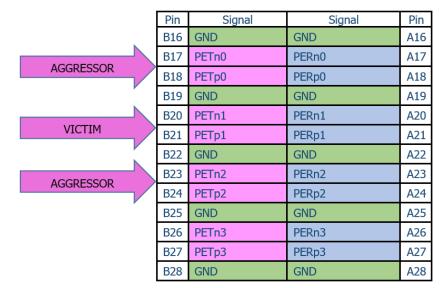

The PET signals (PETp[0..31], PETn[0..31]) on the host shall connect to the PET signals on the connector and the PER signals on the Device Logic. The PER signals (PERp[0..31], PERn[0..31]) on the host shall connect to the PER signals on the connector and the PET signals on the Device Logic. For a high-level wiring diagram, see Figure 6-1.

Lane Polarity Inversion shall be supported on both the host and the device to simplify host and device PCB trace routing constraints.

Lane reversal may be supported on both the host and device. If it is supported, then the transmitting and receiving lanes shall be connected using the same ordering.

PMM follows the same method as OCP NIC 3.0 for determining bifurcation support of a device. *See the Open Compute Project OCP NIC 3.0 Design Specification* for more information.

Figure 6-1. PET and PER Signal Connectivity Between Host and Device

# 6.2.2 Reference Clock (REFCLK[0..3][p/n])

The REFCLKp/REFCLKn signals are used to assist the synchronization of the device's PCI Express interface timing circuits. Refer to the *PCI Express Base Specification* for more details on the functional and tolerance requirements for the reference clock signals.

If SRIS or SRNS is supported by both the system and the device then the reference clock is optional on the host. The reference clock shall be the default configuration on the device. If the reference clock is not detected upon detecting PERST# de-assertion, then the SRIS/SRNS supported device shall switch into SRIS/SRNS mode. The device shall only enter SRNS if the device is configured for this usage through a method outside the scope of this version of the specification.

There are four sets of clock pairs. All devices shall implement REFCLKp0 and REFCLKn0. REFCLKp[1..3] and REFCLKn[1..3] are dependent on device bifurcation support. See Table 6-2 for more details. Note that if x4 bifurcation is needed for a 32 lane PMM device then SRIS/SRNS is required.

It is recommended that the host terminate all reference clocks signals with a pull-down resistor if the clocks are not provided by the host.

# 6.2.3 PERST[0..7]#

Refer to the PCI Express Base Specification for more details on the functional requirements.

All devices and hosts shall implement PERSTO#. PERST[1..7] shall be implemented by the host/device depending on bifurcation support. See Table 6-2 for more details.

| Lane        | PET[03]   | PET[47]   | PET[811]  | PET[1215] | PET[1619] | PET[2023] | PET[2427] | PET[2831] |

|-------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Bifurcation | PER[03]   | PER[47]   | PER[811]  | PER[1215] | PER[1619] | PER[2023] | PER[2427] | PER[2831] |

| 1, x16      | REFCLK0   | REFCLK0   | REFCLK0   | REFCLK0   | NA        | NA        | NA        | NA        |

|             | PERST0#   | PERST0#   | PERST0#   | PERST0#   |           |           |           |           |

| 2, x8       | REFCLK0   | REFCLK0   | REFCLK1   | REFCLK1   | NA        | NA        | NA        | NA        |

| -           | PERST0#   | PERST0#   | PERST1#   | PERST1#   |           |           |           |           |

| 4, x4       | REFCLK0   | REFCLK1   | REFCLK2   | REFCLK3   | NA        | NA        | NA        | NA        |

|             | PERST0#   | PERST1#   | PERST2#   | PERST3#   |           |           |           |           |

| 1, x32      | REFCLK0   |

|             | PERST0#   |

| 2, x16      | REFCLK0   | REFCLK0   | REFCLK0   | REFCLK0   | REFCLK1   | REFCLK1   | REFCLK1   | REFCLK1   |

|             | PERST0#   | PERST0#   | PERST0#   | PERST0#   | PERST1#   | PERST1#   | PERST1#   | PERST1#   |

| 4, x8       | REFCLK0   | REFCLK0   | REFCLK1   | REFCLK1   | REFCLK2   | REFCLK2   | REFCLK3   | REFCLK3   |

|             | PERST0#   | PERST0#   | PERST1#   | PERST1#   | PERST2#   | PERST2#   | PERST3#   | PERST3#   |

| 8, x4       | SRIS/SRNS |

|             | PERST0#   | PERST1#   | PERST2#   | PERST3#   | PERST4#   | PERST5#   | PERST6#   | PERST7#   |

Table 6-2. REFCLK and PERST# Mapping Based on Bifurcation.

# 6.2.4 Reference Clock Outputs (REFCLKOUT[p/n])

REFCLKOUTp/REFCLKOUTn are not supported in this revision of the specification so are reserved for future use. These pins shall be electrically not connected on both host and device.

## 6.2.5 PERSTOUT#

PERSTOUT# is not supported in this revision of the specification so is reserved for future use. These pins shall be electrically not connected on both host and device.

# 6.3 Sideband Signals

## 6.3.1 PRSNT[0..3]#

PRSNT[0..2]# signals indicate physical presence of a device plugged into the host connector and the type of connector on the device. All devices supporting the x4 device connector shall implement PRSNT0#. All devices supporting the x8 device connector shall implement PRSNT0# and PRSNT1#. All devices supporting the x16 device connector shall implement PRSNT0#, PRSNT1#, PRSNT2#. The device shall connect each implemented PRSNT[0..2]# signal to ground.

## 6.3.2 PRSNTB[0..3]#

The PRSNTB[0..3]# are used to detect device presence and provide the host PCIe capability information. The signals shall each be pulled up on the host by a 1 k $\Omega$  resistor. If used on the device, the signals shall have a 200  $\Omega$  series resistor between the card edge and the PRSNTA# signal and shall float if not used. Refer to the *OCP NIC* 3.0 Design Specification for more details on how to configure these resistors.

These signals are shared with PRSNT[0..2]# and RFU signals. Correct detection and configuration of these signals are the responsibility of the host. Not configuring these signals for the correct usage may result in undefined behavior with the device.

## 6.3.3 PRSNTA#

The PRSNTA# signal is used to indicate device presence. It is connected to ground on the host and connected to the PRSNTB[0..3]# pins on the device that are used. Refer to the *OCP NIC 3.0 Design Specification* for more details.

### 6.3.4 GND/EDSFF\_DETECT

The GND/EDSFF\_DETECT signal indicates an EDSFF device is plugged into the host connector. This signal is optional for the host and is only used if the host chooses to support EDSFF devices in a PMM slot. A PMM device shall connect this pin directly to ground. A host that does not support EDSFF devices shall connect this pin directly to ground. If the host supports EDSFF devices then this pin shall have a pull-up resistor greater than 9 k $\Omega$ . If asserted (driven high), then the host should configure its sidebands for EDSFF operation. For more details, see Section 9.2.

### 6.3.5 BIF[0..2]#

BIF[0..2]# are used by the host to configure the bifurcation support of a device. The signal is actively driven by the host.

### 6.3.6 AUX\_PWR\_EN

AUX\_PWR\_EN is asserted by the host to indicate that the host and device are to be in aux power mode and tells the device aux power mode power rails are allowed to be powered. The signal shall be pulled down on the host using a 10 k $\Omega$  resistor.

## 6.3.7 MAIN\_PWR\_EN

MAIN\_PWR\_EN is asserted by the host to indicate that the host and device are to be in main power mode and tells the device main power mode power rails are allowed to be powered. The signal shall be pulled down on the host using a 10 k $\Omega$  resistor.

# 6.3.8 PMM\_PWR\_GOOD

PMM\_PWR\_GOOD is asserted by the device to indicate to the host that power is good when the host initiates the aux power mode or main power mode. The signal shall be pulled down on the host using a 100 k $\Omega$  resistor.

### 6.3.9 PWRBRK#

PWRBRK# is an optional signal. See the *PCI Express Card Electromechanical Specification and the PCI Express Base Specification* for details on the functional requirements for PWRBRK# and transitioning into the Emergency Power Reduction State. If PWRBRK# is supported by the host, then the PWRBRK# pin shall be pulled up on the device with a 9 k $\Omega$  to 60 k $\Omega$  resistor.

This signal is shared with a RFU pin. Correct detection and configuration of this signal is the responsibility of the host. Not configuring the signal for the correct usage may result in undefined behavior with the device.

### 6.3.10 RFU

Signals documented as RFU are reserved for future use. These pins shall be electrically not connected. These pins shall be electrically not connected on both host and device.

### 6.4 M-PESTI

## 6.5 M-PESTI Interface

M-PESTI is not supported in this revision of the specification so are reserved for future use. These pins shall be electrically not connected on both host and device.

# 6.6 2-Wire Interface

### 6.6.1 SMBus Interface

The SMBus interface is a sideband management interface. SMBus is a two-wire interface through which various system component chips communicate with each other and with rest of the system. Refer to the *System Management Bus (SMBus) Specification*.

SMBus is an Open Drain interface. The pull-ups for SMBDATA and SMBCLK shall be on the host and powered within the voltage limits defined for Vddsmb in Table 7-3. The device is allowed to have weak pull-up resistors to protect from floating inputs. If present, then the pull-up resistors on the device are recommended to be greater than or equal to  $45 \text{ k}\Omega$ .

The SMBCLK signal provides the clock signaling from the SMBus initiator to the SMBus target to be able to decode the data on the SMBDATA line.

The SMBDATA signal is used to transfer the data packets between the host and the device according to the SMBus protocol.

## 6.6.2 I3C Basic Interface

The I3C Basic interface is an optional sideband management interface. It is a two-wire interface through which various system component chips communicate with each other and with rest of the system. Refer to the *PCI Express Base Specification* and the *MIPI*<sup>TM</sup> *Alliance Specification for I3C Basic Specification* for more information for more details.

Devices that support I3C Basic shall support SMBus and tolerate SMBus voltage signaling for backwards

#### Pluggable Multipurpose Module Specification

compatibility.

## 6.6.3 SMRST#

The SMRST# signal is an external reset signal for the SMBus interface as defined by the System Management Bus (SMBus) Specification and an external reset for the I3C Basic interface if I3C Basic is supported. SMRST# shall be implemented by the device and is optional for the host. It shall not affect the PCIe interface or other non SMBus/I3C Basic circuit related functions. The device shall have a pull-up resistor greater than or equal to 9 k $\Omega$  on SMRST#.

If the host asserts SMRST#, then the device shall keep the SMBCLK/I3CCLK and SMBDATA/I3CDATA in a high impedance state and ignore any transitions on SMBCLK/I3CCLK and SMBDATA/I3CDATA. When the host de-asserts SMRST#, the device shall place the SMBus or I3C Basic in the SMBus power-on reset state at 3.3 V.

Cycling 3.3 Vaux shall not be used by the host to reset the SMBus or I3C Basic. Cycling 3.3 Vaux may or may not have an effect on the device's SMBus or I3C Basic interface.

### 6.6.4 I3C Basic Output Interface

The I3C Basic output interface is an optional sideband management interface however for these signals the device is the initiator instead of target. It is a two-wire interface through which various system component chips communicate with each other and with rest of the system. Refer to the *MIPI*<sup>TM</sup> *Alliance Specification for I3C Basic Specification* for more information.

# 6.7 SGMII Interface

### 6.7.1 SGMII

SGMII is an optional interface that is used as the primary management interface between the host and device. It's a 4-pin differential interface with 1 differential TX and 1 differential RX. If supported, the host and device shall implement a recovered clock instead of source synchronous clocking. Refer to the *ENG-46158 Serial Gigabit Media Independent Interface Specification* for more details on enumeration, protocol, electricals, and other features.

# 6.8 USB

### 6.8.1 USB\_DATp, USB\_DATn

The USB interface provides an optional sideband interface between host and device. It's a 2-pin differential interface with the device being the endpoint. Refer to the *United Serial Bus (USB) Specification* for more details on enumeration, protocol, electricals, and other features.

## 6.9 Scan Chain

### 6.9.1 Scan Chain Interface

The Scan Chain Interface provides status indication between host and device. Refer to the *OCP NIC 3.0 Design Specification* for more details on functional and timing requirements.

The CLK pin shall be pulled up on the device through a 1 k $\Omega$  resistor. The DATA\_OUT pin shall be pulled down on the device through a 10 k $\Omega$  resistor. The LD# pin shall be pulled up on the device through a 10 k $\Omega$  resistor.

If the host supports the Scan Chain Interface, the DATA\_IN pin shall be pulled up using a 10 k $\Omega$  resistor.

If the host does not support Scan Chain Interface, the CLK pin shall be connected to ground and the DATA\_OUT

#### Pluggable Multipurpose Module Specification

pin shall be pulled down using a 1 k $\Omega$  resistor, and the LD# pin shall be pulled up with a 1 k $\Omega$  resistor.

# 6.10 Connector pinout definitions

Table 6-3 shows the signal pinouts for the connector. These pinouts are shown from the host point of view. Hot plug shall be supported by the device. The contact sequence for each pinout is shown to indicate the order in which the pins make contact to the host. For more details, please refer to *SFF-TA-1037 Connectors for Pluggable Multi-Purpose Module.*

| Pin  | Contact<br>Sequence  | Signal           | Signal     | Contact<br>Sequence  | Pin  |  |  |  |

|------|----------------------|------------------|------------|----------------------|------|--|--|--|

| BH1  | 2 <sup>nd</sup> mate | HP_12 V/HP_48 V  | GND        | 1 <sup>st</sup> mate | AH1  |  |  |  |

|      |                      | Gap              | Gap        |                      |      |  |  |  |

| BO1  | 1 <sup>st</sup> mate | PMM_PWR_GOOD     | PERST2#    | 1 <sup>st</sup> mate | A01  |  |  |  |

| BO2  | 1 <sup>st</sup> mate | MAIN_PWR_EN      | PERST3#    | 2 <sup>nd</sup> mate | AO2  |  |  |  |

| BO3  | 1 <sup>st</sup> mate | LD#              | M-PESTI_IN | 1 <sup>st</sup> mate | AO3  |  |  |  |

| BO4  | 1 <sup>st</sup> mate | DATA_IN          | GND        | 1 <sup>st</sup> mate | AO4  |  |  |  |

| BO5  | 1 <sup>st</sup> mate | DATA_OUT         | SGMII_RXn  | 1 <sup>st</sup> mate | A05  |  |  |  |

| BO6  | 1 <sup>st</sup> mate | CLK              | SGMII_RXp  | 1 <sup>st</sup> mate | A06  |  |  |  |

| BO7  | 1 <sup>st</sup> mate | RFU              | GND        | 1 <sup>st</sup> mate | A07  |  |  |  |

| BO8  | 1 <sup>st</sup> mate | RFU              | SGMII_TXn  | 1 <sup>st</sup> mate | A08  |  |  |  |

| BO9  | 1 <sup>st</sup> mate | RFU              | SGMII_TXp  | 1 <sup>st</sup> mate | A09  |  |  |  |

| BO10 | 1 <sup>st</sup> mate | GND              | GND        | 1 <sup>st</sup> mate | A010 |  |  |  |

| BO11 | 2 <sup>nd</sup> mate | REFCLKn2         | REFCLKn3   | 2 <sup>nd</sup> mate | A011 |  |  |  |

| BO12 | 2 <sup>nd</sup> mate | REFCLKp2         | REFCLKp3   | 2 <sup>nd</sup> mate | A012 |  |  |  |

| BO13 | 1 <sup>st</sup> mate | GND/EDSFF_DETECT | GND        | 1 <sup>st</sup> mate | A013 |  |  |  |

| BO14 | 1 <sup>st</sup> mate | RFU              | RFU        | 1 <sup>st</sup> mate | A014 |  |  |  |

|      |                      | Separator        | Separator  |                      |      |  |  |  |

| B1   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A1   |  |  |  |

| B2   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A2   |  |  |  |

| B3   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A3   |  |  |  |

| B4   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A4   |  |  |  |

| B5   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A5   |  |  |  |

| B6   | 2 <sup>nd</sup> mate | 12 V             | GND        | 1 <sup>st</sup> mate | A6   |  |  |  |

| B7  | 2 <sup>nd</sup> mate | BIFO#      | SMBCLK/I3CCLK    | 2 <sup>nd</sup> mate | A7  |

|-----|----------------------|------------|------------------|----------------------|-----|

| B8  | 2 <sup>nd</sup> mate | BIF1#      | SMBDATA/I3CDATA  | 2 <sup>nd</sup> mate | A8  |

| B9  | 2 <sup>nd</sup> mate | BIF2#      | SMRST#           | 2 <sup>nd</sup> mate | A9  |

| B10 | 2 <sup>nd</sup> mate | PERSTO#    | PRSNTA#          | 2 <sup>nd</sup> mate | A10 |

| B11 | 2 <sup>nd</sup> mate | 3.3 Vaux   | PERST1#          | 2 <sup>nd</sup> mate | A11 |

| B12 | 2 <sup>nd</sup> mate | AUX_PWR_EN | PRSNTO#/PRSNTB2# | 2 <sup>nd</sup> mate | A12 |

| B13 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A13 |

| B14 | 2 <sup>nd</sup> mate | REFCLKn0   | REFCLKn1         | 2 <sup>nd</sup> mate | A14 |

| B15 | 2 <sup>nd</sup> mate | REFCLKp0   | REFCLKp1         | 2 <sup>nd</sup> mate | A15 |

| B16 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A16 |

| B17 | 2 <sup>nd</sup> mate | PETn0      | PERn0            | 2 <sup>nd</sup> mate | A17 |

| B18 | 2 <sup>nd</sup> mate | РЕТрО      | PERp0            | 2 <sup>nd</sup> mate | A18 |

| B19 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A19 |

| B20 | 2 <sup>nd</sup> mate | PETn1      | PERn1            | 2 <sup>nd</sup> mate | A20 |

| B21 | 2 <sup>nd</sup> mate | PETp1      | PERp1            | 2 <sup>nd</sup> mate | A21 |

| B22 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A22 |

| B23 | 2 <sup>nd</sup> mate | PETn2      | PERn2            | 2 <sup>nd</sup> mate | A23 |

| B24 | 2 <sup>nd</sup> mate | PETp2      | PERp2            | 2 <sup>nd</sup> mate | A24 |

| B25 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A25 |

| B26 | 2 <sup>nd</sup> mate | PETn3      | PERn3            | 2 <sup>nd</sup> mate | A26 |

| B27 | 2 <sup>nd</sup> mate | РЕТр3      | PERp3            | 2 <sup>nd</sup> mate | A27 |

| B28 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A28 |

|     |                      | Кеу        | Кеу              |                      |     |

| B29 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A29 |

| B30 | 2 <sup>nd</sup> mate | PETn4      | PERn4            | 2 <sup>nd</sup> mate | A30 |

| B31 | 2 <sup>nd</sup> mate | PETp4      | PERp4            | 2 <sup>nd</sup> mate | A31 |

| B32 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A32 |

| B33 | 2 <sup>nd</sup> mate | PETn5      | PERn5            | 2 <sup>nd</sup> mate | A33 |

| B34 | 2 <sup>nd</sup> mate | РЕТр5      | PERp5            | 2 <sup>nd</sup> mate | A34 |

| B35 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A35 |

| B36 | 2 <sup>nd</sup> mate | PETn6      | PERn6            | 2 <sup>nd</sup> mate | A36 |

| B37 | 2 <sup>nd</sup> mate | РЕТр6      | PERp6            | 2 <sup>nd</sup> mate | A37 |

| B38 | 1 <sup>st</sup> mate | GND        | GND              | 1 <sup>st</sup> mate | A38 |

| B39 | 2 <sup>nd</sup> mate | PETn7      | PERn7            | 2 <sup>nd</sup> mate | A39 |

| B40 | 2 <sup>nd</sup> mate | РЕТр7      | PERp7            | 2 <sup>nd</sup> mate | A40 |

| B41 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A41 |

|-----|----------------------|---------------------|----------|----------------------|-----|

| B42 | 2 <sup>nd</sup> mate | PRSNT1#/PRSNTB0#    | PRSNTB1# | 2 <sup>nd</sup> mate | A42 |

|     |                      | Separator Separator |          |                      |     |

| B43 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A43 |

| B44 | 2 <sup>nd</sup> mate | PETn8               | PERn8    | 2 <sup>nd</sup> mate | A44 |

| B45 | 2 <sup>nd</sup> mate | PETp8               | PERp8    | 2 <sup>nd</sup> mate | A45 |

| B46 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A46 |

| B47 | 2 <sup>nd</sup> mate | PETn9               | PERn9    | 2 <sup>nd</sup> mate | A47 |

| B48 | 2 <sup>nd</sup> mate | РЕТр9               | PERp9    | 2 <sup>nd</sup> mate | A48 |

| B49 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A49 |

| B50 | 2 <sup>nd</sup> mate | PETn10              | PERn10   | 2 <sup>nd</sup> mate | A50 |

| B51 | 2 <sup>nd</sup> mate | PETp10              | PERp10   | 2 <sup>nd</sup> mate | A51 |

| B52 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A52 |

| B53 | 2 <sup>nd</sup> mate | PETn11              | PERn11   | 2 <sup>nd</sup> mate | A53 |

| B54 | 2 <sup>nd</sup> mate | PETp11              | PERp11   | 2 <sup>nd</sup> mate | A54 |

| B55 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A55 |

| B56 | 2 <sup>nd</sup> mate | PETn12              | PERn12   | 2 <sup>nd</sup> mate | A56 |

| B57 | 2 <sup>nd</sup> mate | PETp12              | PERp12   | 2 <sup>nd</sup> mate | A57 |

| B58 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A58 |

| B59 | 2 <sup>nd</sup> mate | PETn13              | PERn13   | 2 <sup>nd</sup> mate | A59 |

| B60 | 2 <sup>nd</sup> mate | PETp13              | PERp13   | 2 <sup>nd</sup> mate | A60 |

| B61 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A61 |

| B62 | 2 <sup>nd</sup> mate | PETn14              | PERn14   | 2 <sup>nd</sup> mate | A62 |

| B63 | 2 <sup>nd</sup> mate | PETp14              | PERp14   | 2 <sup>nd</sup> mate | A63 |

| B64 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A64 |

| B65 | 2 <sup>nd</sup> mate | PETn15              | PERn15   | 2 <sup>nd</sup> mate | A65 |

| B66 | 2 <sup>nd</sup> mate | PETp15              | PERp15   | 2 <sup>nd</sup> mate | A66 |

| B67 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A67 |

| B68 | 2 <sup>nd</sup> mate | I3CCLKOUT           | USB_DATn | 2 <sup>nd</sup> mate | A68 |

| B69 | 2 <sup>nd</sup> mate | I3CDATOUT           | USB_DATp | 2 <sup>nd</sup> mate | A69 |

| B70 | 2 <sup>nd</sup> mate | PRSNT2#/PRSNTB3#    | PWRBRK0# | 2 <sup>nd</sup> mate | A70 |

|     |                      | Gap                 | Gap      |                      |     |

| B71 | 1 <sup>st</sup> mate | GND                 | GND      | 1 <sup>st</sup> mate | A71 |

| B72 | 2 <sup>nd</sup> mate | PETn16              | PERn16   | 2 <sup>nd</sup> mate | A72 |

| B73  | 2 <sup>nd</sup> mate | PETp16 | PERp16 | 2 <sup>nd</sup> mate | A73  |

|------|----------------------|--------|--------|----------------------|------|

| B74  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A74  |

| B75  | 2 <sup>nd</sup> mate | PETn17 | PERn17 | 2 <sup>nd</sup> mate | A75  |

| B76  | 2 <sup>nd</sup> mate | PETp17 | PERp17 | 2 <sup>nd</sup> mate | A76  |

| B77  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A77  |

| B78  | 2 <sup>nd</sup> mate | PETn18 | PERn18 | 2 <sup>nd</sup> mate | A78  |

| B79  | 2 <sup>nd</sup> mate | PETp18 | PERp18 | 2 <sup>nd</sup> mate | A79  |

| B80  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A80  |

| B81  | 2 <sup>nd</sup> mate | PETn19 | PERn19 | 2 <sup>nd</sup> mate | A81  |

| B82  | 2 <sup>nd</sup> mate | PETp19 | PERp19 | 2 <sup>nd</sup> mate | A82  |

| B83  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A83  |

| B84  | 2 <sup>nd</sup> mate | PETn20 | PERn20 | 2 <sup>nd</sup> mate | A84  |

| B85  | 2 <sup>nd</sup> mate | PETp20 | PERp20 | 2 <sup>nd</sup> mate | A85  |

| B86  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A86  |

| B87  | 2 <sup>nd</sup> mate | PETn21 | PERn21 | 2 <sup>nd</sup> mate | A87  |

| B88  | 2 <sup>nd</sup> mate | PETp21 | PERp21 | 2 <sup>nd</sup> mate | A88  |

| B89  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A89  |

| B90  | 2 <sup>nd</sup> mate | PETn22 | PERn22 | 2 <sup>nd</sup> mate | A90  |

| B91  | 2 <sup>nd</sup> mate | PETp22 | PERp22 | 2 <sup>nd</sup> mate | A91  |

| B92  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A92  |

| B93  | 2 <sup>nd</sup> mate | PETn23 | PERn23 | 2 <sup>nd</sup> mate | A93  |

| B94  | 2 <sup>nd</sup> mate | PETp23 | PERp23 | 2 <sup>nd</sup> mate | A94  |

| B95  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A95  |

| B96  | 2 <sup>nd</sup> mate | PETn24 | PERn24 | 2 <sup>nd</sup> mate | A96  |

| B97  | 2 <sup>nd</sup> mate | PETp24 | PERp24 | 2 <sup>nd</sup> mate | A97  |

| B98  | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A98  |

| B99  | 2 <sup>nd</sup> mate | PETn25 | PERn25 | 2 <sup>nd</sup> mate | A99  |

| B100 | 2 <sup>nd</sup> mate | PETp25 | PERp25 | 2 <sup>nd</sup> mate | A100 |

| B101 | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A101 |

| B102 | 2 <sup>nd</sup> mate | PETn26 | PERn26 | 2 <sup>nd</sup> mate | A102 |

| B103 | 2 <sup>nd</sup> mate | PETp26 | PERp26 | 2 <sup>nd</sup> mate | A103 |

| B104 | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A104 |

| B105 | 2 <sup>nd</sup> mate | PETn27 | PERn27 | 2 <sup>nd</sup> mate | A105 |

| B106 | 2 <sup>nd</sup> mate | PETp27 | PERp27 | 2 <sup>nd</sup> mate | A106 |

| B107 | 1 <sup>st</sup> mate | GND    | GND    | 1 <sup>st</sup> mate | A107 |

| B108 | 2 <sup>nd</sup> mate | PETn28      | PERn28    | 2 <sup>nd</sup> mate | A108 |

|------|----------------------|-------------|-----------|----------------------|------|

| B109 | 2 <sup>nd</sup> mate | PETp28      | PERp28    | 2 <sup>nd</sup> mate | A109 |

| B110 | 1 <sup>st</sup> mate | GND         | GND       | 1 <sup>st</sup> mate | A110 |

| B111 | 2 <sup>nd</sup> mate | PETn29      | PERn29    | 2 <sup>nd</sup> mate | A111 |

| B112 | 2 <sup>nd</sup> mate | PETp29      | PERp29    | 2 <sup>nd</sup> mate | A112 |

| B113 | 1 <sup>st</sup> mate | GND         | GND       | 1 <sup>st</sup> mate | A113 |

| B114 | 2 <sup>nd</sup> mate | PETn30      | PERn30    | 2 <sup>nd</sup> mate | A114 |

| B115 | 2 <sup>nd</sup> mate | PETp30      | PERp30    | 2 <sup>nd</sup> mate | A115 |

| B116 | 1 <sup>st</sup> mate | GND         | GND       | 1 <sup>st</sup> mate | A116 |

| B117 | 2 <sup>nd</sup> mate | PETn31      | PERn31    | 2 <sup>nd</sup> mate | A117 |

| B118 | 2 <sup>nd</sup> mate | PETp31      | PERp31    | 2 <sup>nd</sup> mate | A118 |

| B119 | 1 <sup>st</sup> mate | GND         | GND       | 1 <sup>st</sup> mate | A119 |

| B120 | 2 <sup>nd</sup> mate | REFCLKOUTn  | PERST4#   | 2 <sup>nd</sup> mate | A120 |

| B121 | 2 <sup>nd</sup> mate | REFCLKOUTp  | PERST5#   | 2 <sup>nd</sup> mate | A121 |

| B122 | 1 <sup>st</sup> mate | GND         | PERST6#   | 1 <sup>st</sup> mate | A122 |

| B123 | 2 <sup>nd</sup> mate | M-PESTI_OUT | PERST7#   | 2 <sup>nd</sup> mate | A123 |

| B124 | 2 <sup>nd</sup> mate | PRSNT3#     | PERSTOUT# | 2 <sup>nd</sup> mate | A124 |

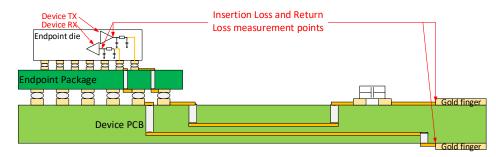

# **7. Electrical Requirements**