# SFF-TA-1005

Specification for

Formatted: Line spacing: Double

Universal Backplane Management (UBM)

Rev 1.4

October 21, 2021

Rev 1.4.1

August 22, 2025

SECRETARIAT: -SFF TA-TWG

This specification is made available for public review at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Comments may be submitted at <a href="https://www.snia.org/feedback">https://www.snia.org/feedback</a>. Comments received will be considered for inclusion in future revisions of this specification.

This document has been released by SNIA. The SFF TWG believes that the ideas, methodologies, and technologies described in this document are technically accurate and are appropriate for widespread distribution.

The description of the connector in this specification does not assure that the specific component is available from connector suppliers. If such a connector component is supplied, it should comply with this specification to achieve interoperability between suppliers.

ABSTRACT: -This specification defines the Universal Backplane Management structure.

POINTS OF CONTACT:

Josh Sinykin/Jason Stuhlsatz

Universal Backplane Management (UBM)

Page 1 Copyright © 20212025 SNIA. All rights reserved.

# SFF-TA-1005 Rev 1.4.1

Broadcom Limited 4385 River Green Parkway\_ Duluth, GA 30096 Ph: 678-728-1406 Email: josh.sinykin@broadcom.com / jason.stuhlsatz@broadcom.com

1

Universal Backplane Management (UBM)

| ĺ                          | PUBLISHEDDRAFT SFF-TA-10                                                                                                                                                                                                                                                                                                                                                                                              | 05 Rev 1.4 <u>.1</u> |   |                                                                   |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---|-------------------------------------------------------------------|

| 1                          | INTELLECTUAL PROPERTY                                                                                                                                                                                                                                                                                                                                                                                                 | •                    |   | Formatted: All caps                                               |

| 2<br>3<br>4<br>5           | The user's attention is called to the possibility that implementation of this specification may require invention covered by patent rights. By distribution of this specification, no position is taken with validity of a claim or claims or of any patent rights in connection therewith.                                                                                                                           |                      |   | Formatted: Font Alignment: Auto                                   |

| 6<br>7<br>8                | This specification is <del>considered SNIA Architecture and is</del> covered by the SNIA IP Policy and as a resul a request for disclosure when it is published.                                                                                                                                                                                                                                                      | t goes through       |   |                                                                   |

| 9<br>10<br>11              | The SNIA IP Review Process is still in progress and is completing on xx xx, xxxx. If IP dis<br>affect this specification are made during this process, this specification may be withdraw                                                                                                                                                                                                                             |                      |   |                                                                   |

| 12<br>13                   | Additional information can be found at the following locations:                                                                                                                                                                                                                                                                                                                                                       | 4-                   |   | Formatted: Font Alignment: Auto                                   |

| 13<br>14<br>15<br>16<br>17 | Results of IP Disclosures: <u>https://www.snia.org/sffdisclosures</u> https://www.snia.org/sffdisclo     SNIA IP Policy: <u>https://www.snia.org/ippolicy</u> SNIA IP Policy: https://www.snia.org/about/corporate_info/ip_policy                                                                                                                                                                                     | <u>sures</u>         |   |                                                                   |

| 18                         | COPYRIGHT                                                                                                                                                                                                                                                                                                                                                                                                             | •                    |   | Formatted: All caps                                               |

| 19                         | The SNIA hereby grants permission for individuals to use this document for personal use only, and for                                                                                                                                                                                                                                                                                                                 |                      |   | Formatted: Font Alignment: Auto                                   |

| 20<br>21<br>22             | and other business entities to use this document for internal use only (including internal copying, di display) provided that:                                                                                                                                                                                                                                                                                        | stribution, and      |   |                                                                   |

|                            | <ol> <li>Any text, diagram, chart, table or definition reproduced shall be reproduced in its e<br/>alteration, and,</li> </ol>                                                                                                                                                                                                                                                                                        | ntirety with no      |   |                                                                   |

|                            | 2. Any document, printed or electronic, in which material from this document (or any po                                                                                                                                                                                                                                                                                                                               |                      |   | Formatted: Font Alignment: Auto                                   |

|                            | reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SI permission for its reuse.                                                                                                                                                                                                                                                                                                   | NIA for granting     |   |                                                                   |

| 23<br>24                   | Other than as explicitly provided above, there may be no commercial use of this document, or sale                                                                                                                                                                                                                                                                                                                     | of any part or       |   | Formatted: Font Alignment: Auto                                   |

| 25<br>26<br>27             | this entire document, or distribution of this document to third parties. All rights not explicitly granted reserved to SNIA.                                                                                                                                                                                                                                                                                          |                      |   |                                                                   |

| 28                         | Permission to use this document for purposes other than those enumerated (Exception) above may                                                                                                                                                                                                                                                                                                                        | be requested         |   |                                                                   |

| 29<br>30                   | by e-mailing <u>copyright request@snia.org</u> . Please include the identity of the requesting individual ar<br>and a brief description of the purpose, nature, and scope of the requested use. Permission for the P                                                                                                                                                                                                  |                      |   | Formatted: Default Paragraph Font, Underline, Font color:<br>Blue |

| 31<br>32<br>33             | not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.                                                                                                                                                          |                      |   |                                                                   |

| 34<br>35                   |                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |   |                                                                   |

| 36                         | DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                            | <b>_</b>             | ~ | Formatted: All caps                                               |

| 37<br>38<br>39<br>40<br>41 | The information contained in this publication is subject to change without notice. The SNIA makes is any kind with regard to this specification, including, but not limited to, the implied warranties of n and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for consequential damages in connection with the furnishing, performance, or use of this specification. | nerchantability      |   | Formatted: Font Alignment: Auto                                   |

| 41<br>42<br>43             | Suggestions for revisions should be directed to <u>https://www.snia.org/feedback/</u> .                                                                                                                                                                                                                                                                                                                               |                      |   | Formatted: Default Paragraph Font, Underline, Font color:<br>Blue |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |   |                                                                   |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |   |                                                                   |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |   |                                                                   |

Universal Backplane Management (UBM)

Page 3 Copyright © 20212025 SNIA. All rights reserved.

#### FOREWORD

1

2

3

5 6

7

8 9

10

11

12

13

14

15 16

17

18 19

20

21

22

23

24

25

26

27

28

29 30

31

32

33

34

35

36

37

38

39

40

41

42 43

44 45

46

47

48

49

50

51

52

53 54

55

56

#### SFF-TA-1005 Rev 1.4.1

The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, <u>as well as since SFF's transition to SNIA in 2016</u>, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at <u>https://www.snia.org/sff/joinhttps://www.snia.org/join</u>.

## **REVISION HISTORY**

Rev 1.0 May 4, 2018

- Initial release

- Rev 1.1 November 16, 2018

- Update to 2Wire\_RESET# signal definition related to 2Wire Mux topology (Table 4-2 and Section 6.2.11)

- Update to PCIe Reset field definition (Section 4.16)

- Update to 2Wire Max Byte Count definition to include 128 and 256 bytes (Section 5.3.1.2.2)

- Update to Operational State field definition (Section 4.20 and 6.2.1)

- Added Clarifying statements to PMDT Read and Write Transactions (Section 6.2.6.1)

- Added Note to Number of Bytes in a Sector Index (Section 6.2.6.2)

- Updated references to sections (incorrect from previous specification)

#### Rev 1.2 April 25, 2019

- Update DFC Status and Control to include an individual change count for each DFC Status and Control Descriptor.

- Fixed error in document. UBM Host uses Read Checksum instead of LCS to check for valid Read response.

- Fixed error in Change Count Command field description.

- Rev 1.3 January 15, 2020

- Updated Section 3 definition of HFC

- Updated Section 4.10 definition of HFC Identity to match Section 3 and Section 4.12

- Updated Section 4.12 with new Figures and expanded language

- Updated Section 4.16 with DFC PERST# Management Override support and field usages

- Updated 5.3.1.2.3 UBM FRU Invalid field description

- Updated Data Byte 4 definition of UBM Port Route Descriptor clarification of bit rates for SAS and PCIe and SATA

- Updated 6.2.9 Backplane Type field description

- Updated 6.2.11 Capabilities Command with DFC PERST# Management Override

- Updated 6.2.12 Features Command with DFC PERST# Management Override

- Updated 6.2.15 Device Off handling description

- Updates Section B.5 Backplane Number and Backplane Type field usages

- Added Appendix C

- Rev 1.4 October 21, 2021

- Updated Signal Definition

- Updated UBM Overview Data Byte 9 Description

- Updated UBM Port Route Descriptor Supported Types (See 6.3.2.2.3)

- Updated Capabilities (See 7.2.11)

- Updated Feature Command (See 7.2.12)

- Updated Change Count Command (See 0)

- Updated Get Non-Volatile Storage Geometry Subcommand definition for the first Sector Index instance. (See 7.2.6.2)

- Fixed broken reference links due to new file formatting

- Various editorial and formatting changes

Changed PwrDIS signal to Power Disable for clarity as signal name changes across various specifications

#### Rev 1.4.1 August 22, 2025

- Added note to Section 5.1 HFC requirements

- Fixed error in UBM Port Route Information Descriptor Table

Universal Backplane Management (UBM)

Page 4 Copyright © <del>2021</del>2025 SNIA. All rights reserved. Formatted: All caps

Formatted: Font Alignment: Auto

Formatted: All caps

Formatted: Font Alignment: Auto

#### SFF-TA-1005 Rev 1.4.1

- Fix missing clause in item d of section 5.16

- Update Max PCIe Link Rates supported \_\_\_\_

- Fix Typo on Page 59 -

- Add Interrupt/Change Count for changes to SES Array Device Slot Element in the DFC S&C -

- Added NICDetect to DFC S&C

- Added Appendix D informative section regarding the OCP and EDSFF detection Added Flex I/O Descriptor Index, and Flex I/O Descriptor S&C -

- \_

- Added Update In Progress Operational State -

- Added Power Event Operational State and Power Event Data Command Add CCC Command, CCC Result Index and CCC Result Descriptor

- Updated section 5.22 CCC with additional figures and examples

11 12 13

10

1

# SFF-TA-1005 Rev 1.4.1

# 2 CONTENTS

| <del>1.</del> - |                                                                 |    |

|-----------------|-----------------------------------------------------------------|----|

| 2               |                                                                 |    |

| 2.              | 2.1 Inductor Documents                                          | 14 |

|                 | 2.2—Sources                                                     |    |

|                 | 2.3—Conventions                                                 | 10 |

| <del>3.</del>   | Keywords, Acronyms, and Definitions                             | 18 |

|                 | 3.1—Keywords                                                    |    |

|                 | 3.2 — Acronyms and Abbreviations                                |    |

|                 | 3.3 Definitions                                                 | 20 |

| 4               | General Description                                             | 2: |

| <del>5.</del>   | Concepts                                                        | 23 |

|                 | 5.1 Host Facing Connector Requirements                          | 23 |

|                 | 5.2 HFC 2WIRE_RESET# signal                                     | 24 |

|                 |                                                                 | 2/ |

|                 | 5.5 — THE FERST # Signal<br>5.4 — UBM FRU Sizing Considerations | 24 |

|                 | 5.5 Wire Davice Topology                                        | 25 |

|                 | 5.5—UBM Controller Initialization Process                       | 27 |

|                 | 5.7—Host UBM Backplane Discovery Process                        | 27 |

|                 | 5.8 CPRSNT# / CHANGE DETECT# signal                             |    |

|                 | 5.9 CHANGE_DETECT# signal interrupt handling                    | 28 |

|                 | 5.10 Host Facing Connector Identity                             |    |

|                 | 5.11. Host Facing Connector Starting Lane                       | 2  |

|                 | 5.12 Chassis Slot Mapping                                       |    |

|                 | 5.13—LED State                                                  |    |

|                 | 5.14 ED Pattern Behavior                                        | 31 |

|                 | 5.15 — Drive Activity Behavior                                  | 31 |

|                 | 5.16 PCIe Clock Routing and PCIe Reset Control Management       |    |

|                 | 5.17 — DEC Status and Control Descriptor                        | 35 |

|                 | 5.18 Bifurcation Port                                           | 35 |

|                 | 5.19 UBM Port Route Information Descriptors                     |    |

|                 | 5.20—UBM Controller Operational State                           | 37 |

|                 | 5.25 UBH Controller Image Update                                | 37 |

| <del>6.</del>   | UBM FRU                                                         | 45 |

|                 | 6.1—UBM FRU 2Wire Protocol                                      |    |

|                 | 6.2—IPMI Defined Data                                           | 46 |

|                 | 6.2 MultiDecorde                                                | 46 |

|                 | 6.3.1—UBM Overview Area                                         |    |

|                 | 6.3.1.1—Beader                                                  | 47 |

|                 | 6.3.1.2Data                                                     | 47 |

|                 | 6.3.1.2.1—Data Byte 0 Definition                                | 47 |

|                 | 6.3.1.2.2 Data Byte 1 Definition                                | 48 |

|                 | 6.3.1.2.3—Data Byte 2 Definition                                | 48 |

|                 | 6.3.1.2.4 Data Byte 3 and Data Byte 4 Definition                | 48 |

|                 | 6.3.1.2.5 Data Byte 5 Definition                                | 48 |

|                 | 6.3.1.2.6 Data Byte 6 Definition                                | 48 |

|                 | 6.3.1.2.7—Data Byte 7 Definition                                | 48 |

|                 | 6.3.1.2.8 Data Byte 8 Definition                                |    |

|                 | 6.3.1.2.9—Data Byte 9 Definition                                | 49 |

|                 | 6.3.1.2.10 — Data Byte 10 Definition                            | 49 |

|                 | 6.3.2—UBM Port Route Information Area                           | 50 |

|                 |                                                                 |    |

Universal Backplane Management (UBM)

Page 6 Copyright © 20212025 SNIA. All rights reserved.

# SFF-TA-1005 Rev 1.4.1

|     | TUBLISTED DKAFT SFF-1A-10                                                   | 05 Rev 1.4 <u>.1</u> |

|-----|-----------------------------------------------------------------------------|----------------------|

| 1   | 6.3.2.1—Header                                                              | 50                   |

|     | 6.3.2.2—Data                                                                | 51                   |

| 2   |                                                                             |                      |

| 3   | 6.3.2.2.1 Data Byte 0 Definition                                            | 51                   |

| 4   | 0.5.2.2.2 Data byte i bennition                                             |                      |

| 5   | 6.3.2.2.3 Data Byte 2 Definition                                            | 52                   |

| 6   |                                                                             |                      |

| 7   | 6.3.2.2.5 Data Byte 4 Definition                                            | 54                   |

| 8   | 6.3.2.2.6 Data Byte 5 Definition                                            | 54                   |

| 9   | 6.3.2.2.7—Data Byte 6 Definition                                            | 54                   |

|     |                                                                             |                      |

| 10  | 7.—_UBM Controller                                                          | 55                   |

| 11  | 7.1—2Wire Protocol                                                          | 55                   |

| 12  | 7.2—JBM Controller Commands                                                 | 57                   |

| 13  | 7.2.1—Operational State Command                                             | 58                   |

| 14  | 7.2.2—Last Command Status Command                                           | 58                   |

| 15  | 7.2.3—Silicon Identity and Version Command                                  | 59                   |

| 16  | 7.2.4—Programmable Update Mode Capabilities Command                         | 61                   |

|     |                                                                             |                      |

| 17  | 7.2.5 Enter Programmable Update Mode Command (Optional)                     | 61                   |

| 18  | 7.2.6 Programmable Mode Data Transfer Command (Optional)                    |                      |

| 19  | 7.2.6.1—2 Wire Variable Length Transactions                                 | 63                   |

| 20  | 7.2.6.2—Get Non Volatile Storage Geometry Subcommand                        | 64                   |

| 21  | 7.2.6.3—Erase Subcommand                                                    | 65                   |

| 22  | 7.2.6.4 Erase Status Subcommand                                             | 66                   |

| 23  | 7.2.6.5—Program Subcommand                                                  | 67                   |

| 24  | 7.2.6.6—Program Status Subcommand                                           | 68                   |

| 25  | 7.2.6.7—Verify Subcommand                                                   | 68                   |

| 26  | 7.2.6.8 Verify Status Subcommand                                            | 69                   |

|     | 7.2.0.0—Verify Status Subcommand                                            | 05                   |

| 27  | 7.2.6.9 Verify Image Subcommand                                             | 70                   |

| 28  | 7.2.6.10 Verify Image Status Subcommand                                     | 70                   |

| 29  | 7.2.0.11—Set Active Image Subcommand                                        | /1                   |

| 30  | 7.2.6.12—Active Image Status Subcommand                                     | 71                   |

| 31  | 7.2.7—Exit Programmable Update Mode Command (Optional)                      | 72                   |

| 32  | 7.2.8—Host Facing Connector Info Command                                    | 72                   |

| 33  | 7.2.9—Backplane Info Command                                                |                      |

| 34  | 7.2.10—Starting Slot Command                                                | 73                   |

| 35  | 7.2.11 — Capabilities Command                                               | 73                   |

| 36  | 7.2.12—Features Command                                                     | 75                   |

| 37  | 7.2.12—Change Count Command                                                 | 77                   |

|     |                                                                             | 78                   |

| 38  | 7.2.14 DFC Status and Control Descriptor Index Command                      |                      |

| 39  | 7.2.15—DFC Status and Control Descriptor Command                            | 79                   |

| 40  | Annandiy A. (Informative) Heat Facing Connector Sidebard Cignal Assignments | 00                   |

| 40  | Appendix A. (Informative) Host Facing Connector Sideband Signal Assignments |                      |

| 41  | A.1—Host Facing Connector Sideband Signal Assignments                       |                      |

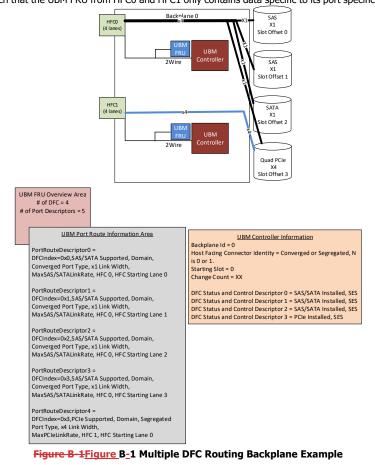

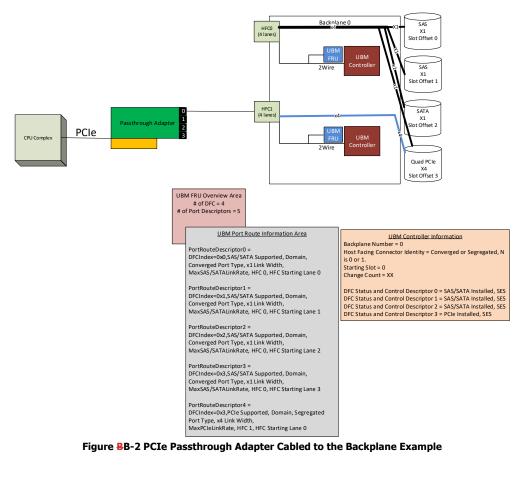

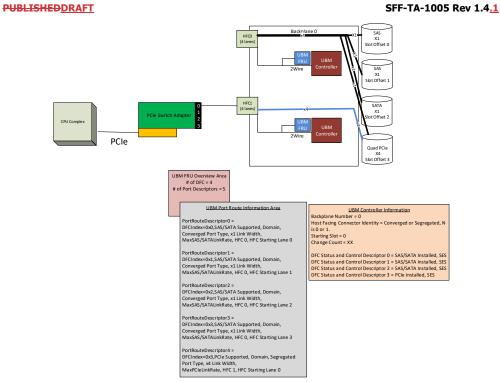

| 42  | Appendix B.— (Informative) Backplane Examples                               | 00                   |

| 42  |                                                                             |                      |

| 43  | B.1.—Backplane Routing                                                      |                      |

| 44  | B.2. Adapters cabled to the Backplane                                       | 90                   |

| 45  |                                                                             |                      |

| 46  | B.1.—SAS Expander on the Backplane                                          | 24                   |

| 47  | B.5. Multiple Backplanes in the Chassis                                     | 94                   |

|     |                                                                             |                      |

| 48  | Appendix C.— (Informative) Host Considerations                              | 97                   |

|     |                                                                             |                      |

| 49  | 1. Scope                                                                    | 15                   |

| = 6 |                                                                             |                      |

| 50  | 2. References                                                               | 16                   |

| 51  | 2.1 Industry Documents                                                      | 16                   |

| 52  | 2.2 Sources                                                                 | 16                   |

|     |                                                                             |                      |

Universal Backplane Management (UBM)

Page 7 Copyright © 20212025 SNIA. All rights reserved.

|          | PU        | IBLISHEDDRAFT                                                                          | SFF-TA-1005 Rev 1.4 <u>.1</u> |

|----------|-----------|----------------------------------------------------------------------------------------|-------------------------------|

| 1        |           | 2.3 Conventions                                                                        | 16                            |

| 2        | 3.        | Keywords, Acronyms, and Definitions                                                    | 18                            |

| 3        | <u>J.</u> | 3.1 Keywords                                                                           | 13                            |

| 4        |           | 3.2 Acronyms and Abbreviations                                                         |                               |

| 5        |           | 3.3 Definitions                                                                        | 20                            |

| 6        | 4.        | General Description                                                                    | 21                            |

| 7        | 5.        | Concepts                                                                               | 23                            |

| 8        | <u>J.</u> | 5.1 Host Facing Connector Requirements                                                 |                               |

| 9        |           | 5.2 HFC 2WIRE_RESET# signal                                                            | 23                            |

| 10       |           | 5.3 HFC PERST# signal                                                                  |                               |

| 11       |           | 5.4 UBM FRU Sizing Considerations                                                      |                               |

| 12       |           | 5.5 2Wire Device Topology                                                              |                               |

| 13       |           | 5.6 UBM Controller Initialization Process                                              | 27                            |

| 14       |           | 5.7 Host UBM Backplane Discovery Process                                               | 27                            |

| 15       |           | 5.8 CPRSNT# / CHANGE DETECT# signal                                                    | 28                            |

| 16       |           | 5.9 CHANGE DETECT# signal interrupt handling                                           | 28                            |

| 17       |           | 5.10 Host Facing Connector Identity                                                    | 28                            |

| 18       |           | 5.11 Host Facing Connector Starting Lane                                               | 29                            |

| 19       |           | 5.12 Chassis Slot Mapping                                                              |                               |

| 20       |           | 5.13 LED State                                                                         |                               |

| 21       |           | 5.14 LED Pattern Behavior                                                              |                               |

| 22       |           | 5.15 Drive Activity Behavior                                                           |                               |

| 23       |           | 5.16 PCIe Clock Routing and PCIe Reset Control Management                              | 31                            |

| 24<br>25 |           | 5.17         DFC Status and Control Descriptor           5.18         Bifurcation Port | 35<br>35                      |

| 25<br>26 |           | 5.10 UBM Port Route Information Descriptors                                            |                               |

| 20       |           | 5.20 UBM Controller Operational State                                                  |                               |

| 28       |           | 5.21 UBM Controller Image Update                                                       |                               |

| 29       |           | 5.22 Cable Contiguous Check (CCC) Process                                              |                               |

| 30       | 6         | UBM FRU                                                                                | 45                            |

| 31       | <u>.</u>  | 6.1 UBM FRU 2Wire Protocol                                                             | 13                            |

| 32       |           | 6.2 IPMI Defined Data                                                                  |                               |

| 33       |           | 6.3 MultiRecords                                                                       |                               |

| 34       |           | 6.3.1 UBM Overview Area                                                                | 47                            |

| 35       |           | 6.3.1.1 Header                                                                         | 47                            |

| 36       |           | 6.3.1.2 Data                                                                           | 47                            |

| 37       |           | 6.3.1.2.1 Data Byte 0 Definition                                                       |                               |

| 38       |           | 6.3.1.2.2 Data Byte 1 Definition                                                       |                               |

| 39       |           | 6.3.1.2.3 Data Byte 2 Definition                                                       | 48                            |

| 40       |           | 6.3.1.2.4 Data Byte 3 and Data Byte 4 Definition                                       | 48                            |

| 41       |           | 6.3.1.2.5 Data Byte 5 Definition                                                       |                               |

| 42       |           | 6.3.1.2.6 Data Byte 6 Definition                                                       |                               |

| 43       |           | 6.3.1.2.7 Data Byte 7 Definition                                                       | 48                            |

| 44<br>45 |           | 6.3.1.2.8 Data Byte 8 Definition                                                       | 49<br>49                      |

| 45<br>46 |           | 6.3.1.2.9 Data Byte 9 Definition                                                       |                               |

| 40<br>47 |           | 6.3.1.2.10 Data Byte 10 Definition<br>6.3.2 UBM Port Route Information Area            | 49<br>50                      |

| 47<br>48 |           | 6.3.2.1 Header                                                                         |                               |

| 49       |           | 6.3.2.2 Data                                                                           | 50                            |

| 50       |           | 6.3.2.2.1 Data Byte 0 Definition                                                       |                               |

| 51       |           | 6.3.2.2.2 Data Byte 1 Definition                                                       |                               |

| 52       |           | 6.3.2.2.3 Data Byte 2 Definition                                                       | 52                            |

| 53       |           | 6.3.2.2.4 Data Byte 3 Definition                                                       | 52                            |

|          |           |                                                                                        |                               |

Universal Backplane Management (UBM)

Page 8 Copyright © 20212025 SNIA. All rights reserved.

l

| I        | PUBLISHEDDRAFT                                                                                                                                       | SFF-TA-1005 Rev 1.4 <u>.1</u> |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1        | 6.3.2.2.5 Data Byte 4 Definition                                                                                                                     | 54                            |

| 2        | 6.3.2.2.6 Data Byte 5 Definition                                                                                                                     | 54                            |

| 3        | 6.3.2.2.7 Data Byte 6 Definition                                                                                                                     | 54                            |

|          | 7 UDM Controller                                                                                                                                     | 55                            |

| 4        | 7. UBM Controller<br>7.1 2Wire Protocol                                                                                                              | 55<br>55                      |

| 5<br>6   | 7.1 2Wire Protocol<br>7.2 UBM Controller Commands                                                                                                    |                               |

| 7        | 7.2 Obm Controller Command                                                                                                                           | 57                            |

| 8        | 7.2.2 Last Command Status Command                                                                                                                    | 58                            |

| 9        | 7.2.3 Silicon Identity and Version Command                                                                                                           | 50                            |

| 10       | 7.2.4 Programmable Update Mode Capabilities Command                                                                                                  | 55                            |

| 11       | 7.2.5 Enter Programmable Update Mode Command (Optional)                                                                                              | 61                            |

| 12       | 7.2.6 Programmable Mode Data Transfer Command (Optional)                                                                                             | 62                            |

| 13       | 7.2.6.1 2 Wire Variable Length Transactions                                                                                                          | 63                            |

| 14       | 7.2.6.2 Get Non-Volatile Storage Geometry Subcommand                                                                                                 | 64                            |

| 15       | 7.2.6.3 Erase Subcommand                                                                                                                             | 65                            |

| 16       | 7.2.6.4 Erase Status Subcommand                                                                                                                      | 66                            |

| 17       | 7.2.6.5 Program Subcommand                                                                                                                           | 67                            |

| 18       | 7.2.6.6 Program Status Subcommand                                                                                                                    | 68                            |

| 19       | 7.2.6.7 Verify Subcommand                                                                                                                            | 68                            |

| 20       | 7.2.6.8 Verify Status Subcommand                                                                                                                     | 69                            |

| 21       | 7.2.6.9 Verify Image Subcommand                                                                                                                      | 70                            |

| 22       | 7.2.6.10 Verify Image Status Subcommand                                                                                                              | 70                            |

| 23       | 7.2.6.11 Set Active Image Subcommand                                                                                                                 | 71                            |

| 24       | 7.2.6.12 Active Image Status Subcommand                                                                                                              | 71                            |

| 25       | 7.2.7 Exit Programmable Update Mode Command (Optional)                                                                                               | 72                            |

| 26       | 7.2.8 Host Facing Connector Info Command                                                                                                             | 72                            |

| 27       | 7.2.9 Backplane Info Command                                                                                                                         | 73                            |

| 28       | 7.2.10 Starting Slot Command                                                                                                                         | 73                            |

| 29       | 7.2.11 Capabilities Command                                                                                                                          | 73                            |

| 30       | 7.2.12 Features Command                                                                                                                              | 75                            |

| 31       | 7.2.13 Change Count Command                                                                                                                          | 77                            |

| 32<br>33 | 7.2.14 DFC Status and Control Descriptor Index Command                                                                                               | 78<br>78                      |

| 33<br>34 | 7.2.15         Cable Contiguous Check (CCC) Command (Optional)           7.2.16         Cable Contiguous Check (CCC) Result Index Command (Optional) |                               |

| 34<br>35 | 7.2.17 DFC Status and Control Descriptor Command                                                                                                     | 79<br>79                      |

| 36       | 7.2.17 Cable Contiguous Check (CCC) Result Descriptor Command (Optional)                                                                             |                               |

| 30       | 7.2.19 Flex I/O Status and Control Descriptor Index Command (Optional)                                                                               | 81                            |

| 38       | 7.2.20 Flex I/O Status and Control Descriptor Index Command (Optional)                                                                               |                               |

| 39       | 7.2.21 Power Event Data Command (Optional)                                                                                                           | 0 <del>4</del><br>87          |

| 55       |                                                                                                                                                      | 0/                            |

| 40       | Appendix A. (Informative) Host Facing Connector Sideband Signal Assignments                                                                          | 88                            |

| 41       | A.1 Host Facing Connector Sideband Signal Assignments                                                                                                | 88                            |

|          |                                                                                                                                                      |                               |

| 42       | Appendix B. (Informative) Backplane Examples                                                                                                         |                               |

| 43       | B.1. Backplane Routing                                                                                                                               | 89                            |

| 44       | B.2. Adapters cabled to the Backplane                                                                                                                |                               |

| 45       | B.3. PCIe Switch on the Backplane                                                                                                                    | 93                            |

| 46<br>47 | B.4. SAS Expander on the Backplane                                                                                                                   | 94<br>94                      |

|          | B.5. Multiple Backplanes in the Chassis                                                                                                              |                               |

| 48       | Appendix C. (Informative) Host Considerations                                                                                                        | 97                            |

| 49       | Appendix D. (Informative) OCP NIC and EDSFF/SFF-TA-1009 UBM Handling                                                                                 | 98                            |

| 50       |                                                                                                                                                      |                               |

| 51       |                                                                                                                                                      |                               |

Universal Backplane Management (UBM)

Page 9 Copyright © 20212025 SNIA. All rights reserved.

# SFF-TA-1005 Rev 1.4.1

| 1        | FIGURES                                                                                                                                            |               |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

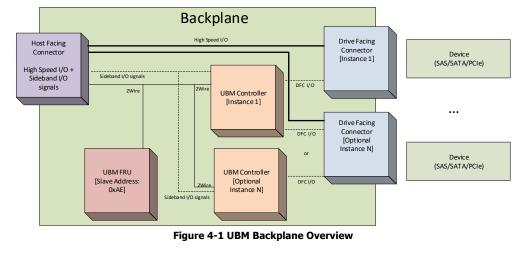

| 2        | Figure 4-1 UBM Backplane Overview                                                                                                                  | <del>12</del> |

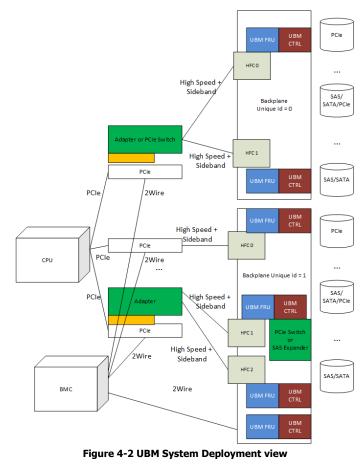

| 3        | Figure 4 2 UBM System Deployment view                                                                                                              |               |

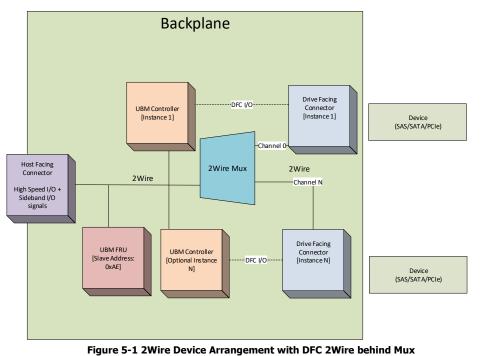

| 4        | Figure 5 1 2Wire Device Arrangement with DFC 2Wire behind Mux                                                                                      | <del></del>   |

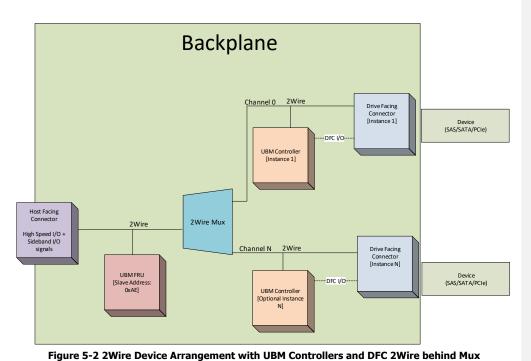

| 5        | Figure 5-2 2Wire Device Arrangement with UBM Controllers and DEC 2Wire behind Mux                                                                  | 17            |

| 6        | Figure 5-3 Example of Multiple Backplanes Managed by One Managed Resource                                                                          | 21            |

| 7        | Figure 5.4 Example of Multiple Rackplanes Managed by Two Separate Managed Resources                                                                | 21            |

| 8        | Figure 6 1 UBM FRU Format                                                                                                                          |               |

| 9        | Figure C. 2 UDM EDU 2Wing Dood Transportion                                                                                                        | 20            |

| 10       | Figure 6-2 UBM FRU 2Wire Write Transaction                                                                                                         |               |

| 11       | Figure 7.1 LIBM Controller Write Transaction                                                                                                       | 20            |

| 12       | Figure 7 2 UBM Controller Read Transaction                                                                                                         |               |

| 13       | Figure 7.2 UPM Controller DMDT Write Transaction                                                                                                   | 45            |

| 14       | Figure 7-4 UBM Controller PMDT Read Transaction                                                                                                    |               |

| 15       | Figure 7 5 Non Velatile Storage Coometry Diagram                                                                                                   | 16            |

| 16       | Figure 9 1 Multiple DFC Routing Backplane Example                                                                                                  |               |

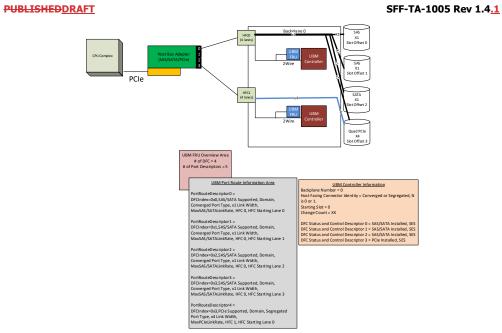

| 17       | Figure B-2 PCIe Passthrough Adapter Cabled to the Backplane Example                                                                                |               |

| 18       | Figure B-3 PCIe Switch Adapter Cabled to the Backplane Example                                                                                     |               |

| 19       | Figure B 4 Host Bus Adapter Cabled to the Backplane Example                                                                                        |               |

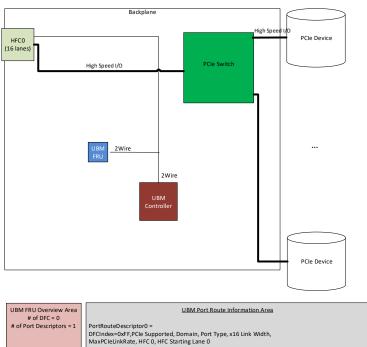

| 20       | Figure B 5 PCIe Switch on the Backplane Example                                                                                                    |               |

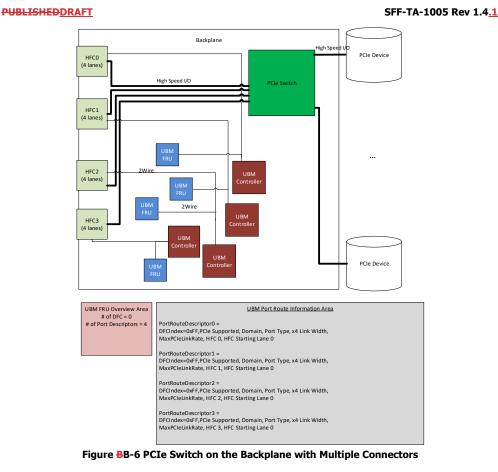

| 20       | Figure B-5 PCIe Switch on the Backplane with Multiple Connectors                                                                                   |               |

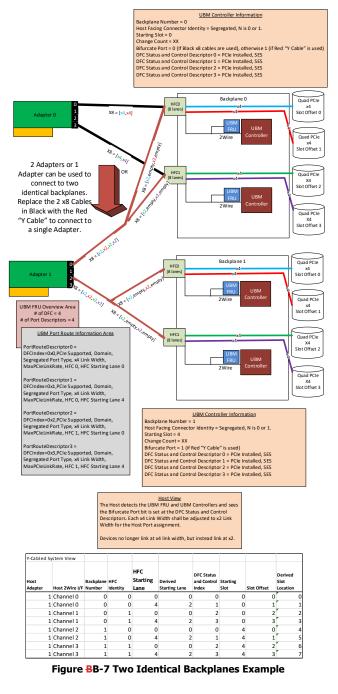

| 21       | Figure B-7 Two Identical Backplanes Example                                                                                                        |               |

| 22       | Figure 3-7 Two Identical Backplanes Example<br>Figure 4-1 UBM Backplane Overview                                                                   | 21            |

| 23<br>24 | Figure 4-2 UBM System Deployment view                                                                                                              | 21            |

| 24<br>25 |                                                                                                                                                    | 22            |

|          | Figure 5-1 2Wire Device Arrangement with DFC 2Wire behind Mux<br>Figure 5-2 2Wire Device Arrangement with UBM Controllers and DFC 2Wire behind Mux |               |

| 26<br>27 | Figure 5-2 Example of Multiple Backplanes Managed by One Managed Resource                                                                          | 26<br>30      |

|          |                                                                                                                                                    |               |

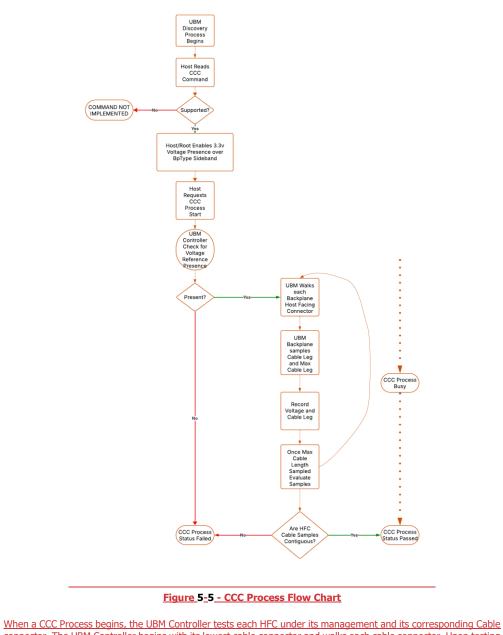

| 28       | Figure 5-4 Example of Multiple Backplanes Managed by Two Separate Managed Resources<br>Figure 5-5 - CCC Process Flow Chart                         |               |

| 29       |                                                                                                                                                    | 39            |

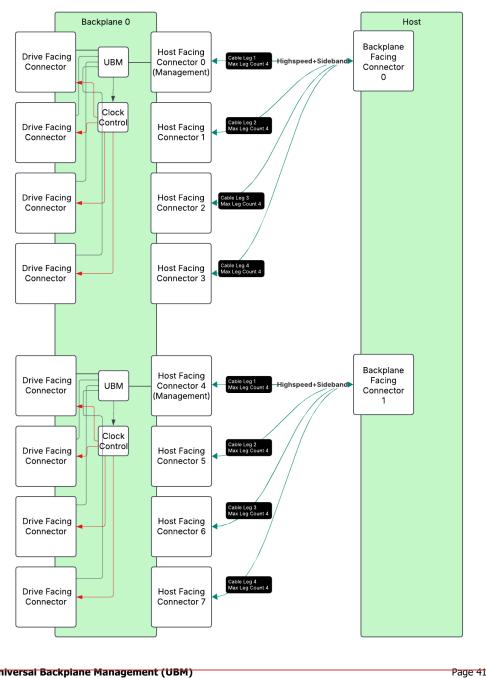

| 30       | Figure 5-6 - Two Cable Scenario Diagram                                                                                                            | 42            |

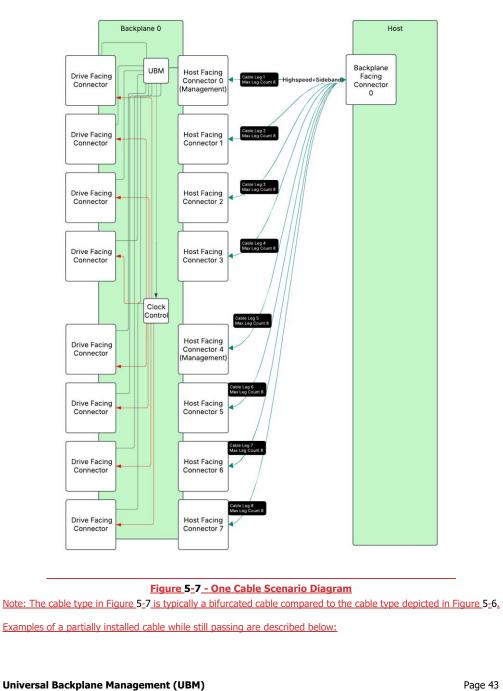

| 31       | Figure 5-7 - One Cable Scenario Diagram                                                                                                            | 43            |

| 32       | Figure 6-1 UBM FRU Format                                                                                                                          | 45            |

| 33       | Figure 6-2 UBM FRU 2Wire Read Transaction                                                                                                          | 46            |

| 34       | Figure 6-3 UBM FRU 2Wire Write Transaction                                                                                                         | 46            |

| 35       | Figure 7-1 UBM Controller Write Transaction                                                                                                        | 55            |

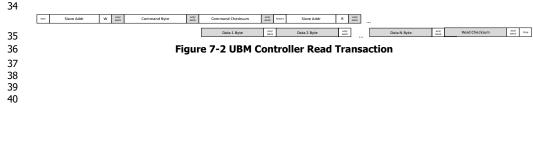

| 36       | Figure 7-2 UBM Controller Read Transaction                                                                                                         | 55            |

| 37       | Figure 7-3 UBM Controller PMDT Write Transaction                                                                                                   | 63            |

| 38       | Figure 7-4 UBM Controller PMDT Read Transaction                                                                                                    | 63            |

| 39       | Figure 7-5 Non-Volatile Storage Geometry Diagram                                                                                                   | 64            |

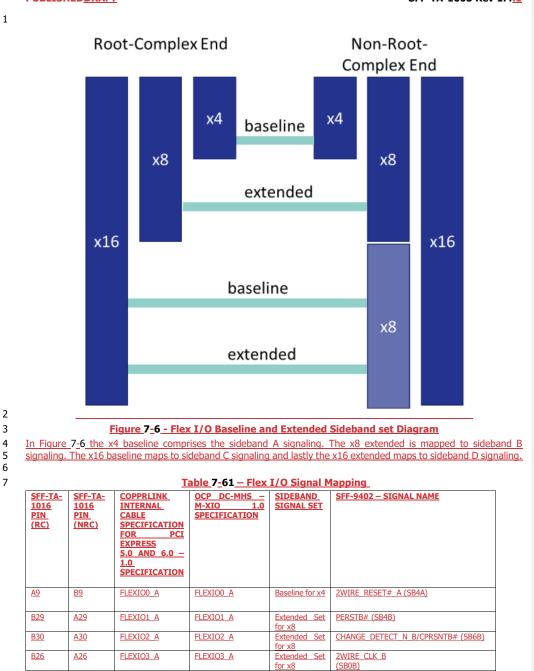

| 40       | Figure 7-6 - Flex I/O Baseline and Extended Sideband set Diagram                                                                                   | 83            |

| 41       | Figure B-1 Multiple DFC Routing Backplane Example                                                                                                  | 89            |

| 42       | Figure B-2 PCIe Passthrough Adapter Cabled to the Backplane Example                                                                                | 90            |

| 43       | Figure B-3 PCIe Switch Adapter Cabled to the Backplane Example                                                                                     | 91            |

| 44       | Figure B-4 Host Bus Adapter Cabled to the Backplane Example                                                                                        | 92            |

| 45       | Figure B-5 PCIe Switch on the Backplane Example                                                                                                    |               |

| 46       | Figure B-6 PCIe Switch on the Backplane with Multiple Connectors                                                                                   |               |

| 47       | Figure B-7 Two Identical Backplanes Example                                                                                                        | 95            |

| 48       |                                                                                                                                                    |               |

| 49       | TABLES                                                                                                                                             |               |

| 50       | Table 5 1 Host Facing Connector Sideband Signal Requirements                                                                                       |               |

| 50 | Table 5-1 Host Facing Connector Sideband Signal Requirements                                        | <b>T</b> 1     |

|----|-----------------------------------------------------------------------------------------------------|----------------|

| 51 | Table 5-2 Host And UBM Controller 2WIRE_RESET# Timing                                               | <del>-15</del> |

| 52 | Table 5-3 UBM FRU Memory Size Considerations                                                        | <del>-15</del> |

| 53 | Table 5-4 HFC Starting Lane Example of 2x2 DFC to 1 HFC                                             | -20            |

| 54 | Table 5-5 Access Map to Find Actual Slot Location                                                   | -20            |

| 55 | Table 5. 6 DCIa Clock Pouting And DCIa Parat Control Management (No DEC DEDST# Management Override) | 24             |

55

Table 5-6 PCIe Clock Routing And PCIe Reset Control Management (No DFC PERST# Management Override)

24

56

Table 5-7 PCIe Clock Routing And PCIe Reset Control Management (DFC PERST# Management Override Set

24

Universal Backplane Management (UBM)

Page 10 Copyright © 20212025 SNIA. All rights reserved.

|                      | PUBLISHEDDRAFT                                                                                                                    | SFF-TA-1005 Rev 1.4 <u>.1</u> |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 1                    | to 1h and override supported)                                                                                                     |                               |

| 2                    | Table 5 8 PCIe Clock Routing and PCIe Reset Control Management (DFC PERST# Mana                                                   |                               |

| 3                    | override supported)                                                                                                               |                               |

| 4                    | Table 5-9 SFF 8639 Connector Port Usages                                                                                          |                               |

| 5                    | Table 5 10 SFF TA 1001 Connector Port Usages                                                                                      |                               |

| 6                    | Table 6 1 UBM FRU 2Wire Transaction Legend                                                                                        |                               |

| 7                    | Table 6 2 UBM Overview Area                                                                                                       |                               |

| 8                    | Table 6 3 UBM Overview Area: Data Byte 0 Definition                                                                               | <u> </u>                      |

| 9                    | Table 6 4 UBM Overview Area: Data Byte 1 Definition                                                                               | 32                            |

| 10                   | Table 6 5 UBM Overview Area: Data Byte 2 Definition                                                                               | 32                            |

| 11                   | Table 6 6 UBM Overview Area: Data Byte 5 Definition                                                                               | 32                            |

| 12                   | Table 6 7 UBM Overview Area: Data Byte 6 Definition                                                                               | 32                            |

| 13                   | Table 6.9. UPM Overview Areas Data Pite 7 Definition                                                                              |                               |

| 14                   | Table 6-9 UBM Overview Area: Data Byte 8 Definition                                                                               |                               |

| 15                   | Table 6 10 UBM Overview Area: Data Byte 9 Definition                                                                              | 33                            |

| 16                   | Table 6 11 UBM Port Route Information Area                                                                                        | <u>34</u>                     |

| 17                   | Table 6-12 UBM Port Route Information Descriptor                                                                                  |                               |

| 18                   | Table 6 12 Obier for Route Information: Data Byte 0 Definition                                                                    |                               |

| 19                   | Table 6 14 Port Route Information: Data Byte 1 Definition                                                                         |                               |

| 20                   | Table 6-15 Port Route Information: Data Byte 1 Definition                                                                         |                               |

| 20                   | Table 6-16 Port Route Information: Data Byte 3 Definition                                                                         |                               |

| 21                   | Table 6-17 Port Route Information: Data Byte 3 Definition                                                                         | 30                            |

| 22                   | Table 6-18 Port Route Information: Data Byte 5 Definition                                                                         | 37                            |

| 23<br>24             | Table 6 19 Port Route Information: Data Byte 5 Definition                                                                         |                               |

| 2 <del>4</del><br>25 | Table 7 1 UBM Controller 2wire Transaction Legend                                                                                 | 38                            |

| 25<br>26             | Table 7 2 UBM Controller Successful Read Transaction Sequence                                                                     |                               |

| 20                   | Table 7-2 UBM Controller Successful Write Transaction Sequence                                                                    | 39                            |

| 27                   | Table 7 4 UBM Controller Invalid Write Transaction Sequence                                                                       | 39                            |

| 20<br>29             | Table 7 5 UBM Controller Invalid Write Transaction Sequence                                                                       |                               |

|                      | Table 7 5 OBM Controller Invalid Redu Transaction Sequence                                                                        | 40                            |

| 30                   |                                                                                                                                   |                               |

| 31<br>32             | Table 7 7 Operational State Command Table 7 8 Operational State Command Descriptions                                              |                               |

|                      | Table 7-8 Operational State Command Descriptions<br>Table 7-9 Last Command Status Command                                         | 41                            |

| 33                   | Table 7 10 Last Command Status Command<br>Table 7 10 Last Command Status Descriptions                                             | 41                            |

| 34<br>35             |                                                                                                                                   | 42                            |

|                      | Table 7 11 Silicon Identity and Version Command                                                                                   |                               |

| 36                   | Table 7 12 UBM Specification Version (Examples)                                                                                   | <u>42</u>                     |

| 37                   | Table 7 13 Programming Update Mode Capabilities Command                                                                           | 43                            |

| 38                   | Table 7 14 Programming Update Mode Capabilities: Data Byte 0 Definition           Table 7 15 Enter Programing Update Mode Command | 43                            |

| 39                   | Table 7-15 Enter Programing Update Mode Command                                                                                   |                               |

| 40                   | Table 7 16 PMDT Write Format<br>Table 7 17 Programmable Mode Subcommands                                                          | <u> </u>                      |

| 41                   |                                                                                                                                   |                               |

| 42                   | Table 7 18 PMDT Read Format                                                                                                       | 45                            |

| 43                   | Table 7 19 Programmable Mode Status                                                                                               | 45                            |

| 44                   | Table 7 20 PMDT Write Format for the Get Non Volatile Storage Geometry Subcomman                                                  |                               |

| 45                   | Table 7 21 PMDT Read Format for the Get Non Volatile Storage Geometry Subcomman                                                   |                               |

| 46                   | Table 7 22 PMDT Write Format for the Erase Subcommand                                                                             | 47                            |

| 47                   | Table 7 23 PMDT Write Format for the Erase Status Subcommand                                                                      |                               |

| 48                   | Table 7 24 PMDT Read Format for the Erase Status Subcommand                                                                       | 48                            |

| 49                   | Table 7 25 THET Write Format for the Hogram Subcommand                                                                            | -12                           |

| 50                   |                                                                                                                                   | <del>50</del>                 |

| 51                   | Table 7 27 PMDT Read Format for the Program Status Subcommand                                                                     | <del></del>                   |

| 52                   | Table 7 28 PMDT Write Format for the Verify Subcommand                                                                            | <del>50</del>                 |

| 53                   | Table 7 25 THDT Write Format for the Verity Status Subcommand                                                                     | <del>51</del>                 |

| 54                   | Table 7 30 PMDT Read Format for the Verify Status Subcommand                                                                      | <del>51</del>                 |

| 55                   | Table 7 31 PMDT Write Format for the Verify Image Subcommand                                                                      | <del></del>                   |

| 56                   | Table 7 32 PMDT Write Format for the Verify Image Status Subcommand                                                               | <del></del>                   |

|                      |                                                                                                                                   |                               |

Universal Backplane Management (UBM)

Page 11 Copyright © <del>2021</del>2025 SNIA. All rights reserved.

# SFF-TA-1005 Rev 1.4.1

| 1              | Table 7 33 PMDT Read Format for the Verify Image Status Subcommand                                                                                                                                                                                              | <u>-52</u>                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 2              | Table 7 34 PMDT Write Format for the Set Active Image Subcommand                                                                                                                                                                                                | <del>-53</del><br><del>53</del>    |

| 3              | Table 7 35 PMDT Write Format for the Active Image Status Subcommand                                                                                                                                                                                             | <del>- 53</del><br>- <del>53</del> |

| 4              | Table 7 36 PMDT Read Format for the Active Image Status Subcommand                                                                                                                                                                                              | <del>- 53</del><br>54              |

| 5              | Table 7 37 Exit Programmable Update Mode Command                                                                                                                                                                                                                | -54                                |

| 6              | Table 7 38 Host Facing Connector Info Command           Table 7 39 Host Facing Connector Info: Data Byte 0 Definition                                                                                                                                           | -54                                |

| 7              |                                                                                                                                                                                                                                                                 | <del>55</del>                      |

| 8<br>9         | Table 7 40 Backplane Info Command           Table 7 41 Backplane Info: Data Byte 0 Definition                                                                                                                                                                   | <del></del>                        |

|                | Table 7 12 Starting Slot Command                                                                                                                                                                                                                                | <del>-55</del>                     |

| 10             | Table 7 12 Starting Side Command                                                                                                                                                                                                                                | -55                                |

| 11<br>12       | Table 7-15 Capabilities Command<br>Table 7-41 Capabilities Command: Data Byte 0 Definition                                                                                                                                                                      | <del>- 55</del><br><del>56</del>   |

| 12             | Table 7-45 Capabilities Command: Data Byte 1 Definition                                                                                                                                                                                                         | <del>57</del>                      |

| 13             | Table 7-45 Capabilities Command. Data Byte 1 Dennition                                                                                                                                                                                                          | -57                                |

| 15             | Table 7 47 Features Command: Data Byte 0 Definition                                                                                                                                                                                                             | <u>-58</u>                         |