1

2 3 4

4

7 8

6

9 10 11

12 13 14

15 16 17

18 19 20

21222324

25 26 27

28 29

30 31 32

33

34 35

# SFF-8472

Specification for

# **Management Interface for SFP+**

Rev 12.4.3 March 4, 2025

SECRETARIAT: SFF TWG

This specification is made available for public review at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Comments may be submitted at <a href="https://www.snia.org/feedback/">https://www.snia.org/feedback/</a>. Comments received will be considered for inclusion in future revisions of this specification.

This document has been released by SNIA. The SFF TWG believes that the ideas, methodologies, and technologies described in this document are technically accurate and are appropriate for widespread distribution.

ABSTRACT: This specification defines an enhanced digital interface (memory map and management interface) for monitoring and control of SFP+ optical transceivers and similar products.

POINTS OF CONTACT:

Lumentum 1001 Ridder Park Drive

Hock Lim

San Jose, CA 95131 Ph: 408-546-5984

email: hockgin.lim@lumentum.com

Chairman SFF TWG Email: <u>SFF-Chair@snia.org</u>

## Intellectual Property

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published.

The SNIA IP Review Process is still in progress and completing on xxx, 2025. If IP disclosures that affect this specification are made during this process, this specification may be withdrawn.

Additional information can be found at the following locations:

Results of IP Disclosures: https://www.snia.org/sffdisclosures

SNIA IP Policy: <a href="https://www.snia.org/ippolicy">https://www.snia.org/ippolicy</a>

# Copyright

SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <a href="mailto:copyright\_request@snia.org">copyright\_request@snia.org</a>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

#### **Disclaimer**

The information contained in this publication is subject to change without notice. SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to <a href="https://www.snia.org/feedback/">https://www.snia.org/feedback/</a>.

#### **FOREWORD**

1

2

3 4

5 6

7 8 9

10

The development work on this specification was done by the SFF TA TWG, an industry group. Since its formation as the SFF Committee in August 1990, as well as since SFF's transition to SNIA in 2016, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TA TWG, the signup for membership can be found at <a href="https://www.snia.org/join">https://www.snia.org/join</a>.

**Change History**

| Rev.               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date                                   |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.0                | Initial Submission of Document, Preliminary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2001-04-05                             |

| 2.0                | Draft Second Revision, Preliminary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2001-05-18                             |

| 3.0                | Draft Third Revision, Preliminary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2001-06-27                             |

| 4.0                | Draft Fourth Revision, Preliminary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2001-10-08                             |

| 5.0                | Draft Fifth Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2001-11-05                             |

| 6.0                | Draft Sixth Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2001-11-19                             |

| 7.0                | Draft Revision 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2002-01-09                             |

| 8.0                | Draft Revision 8.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2002-02-01                             |

| 9.0                | Draft Revision 9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2002-03-28                             |

| 9.0                | Revision 9.0 Approved for Technical Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2002-05                                |

| 9.2                | Revision 9.2 Submitted for Publication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2002-05-30                             |

| 9.3                | Editorial Modifications to rev. 9.2. 9.3 Submitted for Publication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2002-08-01                             |

| 9.4<br>9.5<br>10.0 | Add extensions to include additional technologies.  Results of Dec.5 03 discussions. Includes:  Support for Multiple Application Selection Reserved values for SFF-8079 in Table 3.1, Table 3.10, Table 3.12, and Table 3.17.  Additional transceiver type values in Table 3.5 Additional values in Table 3.1a, 3.5a and 3.5b Additional values in Table 3.12 General editorial modifications.  Editorial Modifications to rev. 9.4. 9.5 Submitted for Publication.  Add extensions to the following tables: Table 3.1b, 3.2, 3.4, 3.5, 3.5b, 3.7, 3.11, 3.12, 3.21 Editorial changes to the following tables: Table 3.2, 3.3, 3.4, 3.6, 3.7, 3.9, 3.10, 3.17 Add table 3.1a, 3.6a, 3.18a and references to 8079/8431. | 2004-05-26<br>2004-06-01<br>2007-02-06 |

| 10.2               | Editorial updates per ballot feedback. Technical update to Tables 3.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2007-06-01                             |

| 10.3               | Edits per SFF-8431                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2007-12-07                             |

| 10.4               | Edits per SFF-8431, add bits in Table 3.5 and add Tables 3.6b and 3.6c for SFF-8431 and SFF-8461. Add Table 3.1c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2009-01-30                             |

| 11.0               | Edits per FC-PI-5 (16GFC) to tables 3.6a,3.12,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2010-05-21                             |

| 11.1               | Table 3-2 Identifier Values and modified to point to SFF-8024 as the reference for later values and codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2012-10-26                             |

| 11.2               | Added FC-PI-6 to Table 3.6a Rate Identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2013-06-06                             |

| 11.3               | Added OM4 to Table 3.1 and Address A0h, Byte 18. Added 3200 MBytes to Table 3.5 Byte 10 Bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2013-06-11                             |

| Rev.  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Date       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 11.4  | Added optional support for: retimer/CDR in transceiver; Variable Receiver Decision Threshold; Rate Select logic for 10G/8G with bypassable CDRs; Table addressing in upper half of address A2h; Laser temperature and TEC current alarms and warnings; Compliance codes for OTN 2 km, 40 km and 80 km profiles in G.959.1.                                                                                                                                                                                                                                                                                                                                               | 2014-07-24 |

| 11.8  | Introduced a major style change. The addition of Section, Figure, and Table numbering makes correlation of previous Change History difficult for readers, so a Cross Reference of Figures and Tables was prepared.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2014-07-31 |

| 11.9  | Re-defined byte 36 of Table 5-4 Transceiver Compliance Codes to be 'Extended Compliance Codes' Added definitions of the coding formats for optional laser temperature and TEC current to Section 9.2.  Added Table 9-3 and Table 9-4 to illustrate the TEC current two's complement format.  Corrected Table 10-2 Retimer/CDR Rate Select Logic Table 'Bit 64.1 of A2h' to be 'Bit 64.3 of A0h'  Added Byte 64 Bit 5 in Table 8-3 to identify transceivers with Power Level 3 plus:  o Renamed t_power_level2 to t_hpower_level in Table 8-7 and modified the contents of the parameter and conditions cells.  o Changed the description for bits 1 and 0 in Table 10-1. | 2014-08-14 |

| 11.9b | Moved CDR unlocked flags from byte A2h 115 to 119.  Added Tx input EQ and RX output EMPH to bytes A2h 114-115  Added Tables 9-13 and 9-14 Tx input EQ and Rx output EMPH values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2014-08-27 |

| 12.0  | The mix of references to tables and pages was reduced to use only pages Consolidated the two figures in Section 4 into one. Corrected Table 4-4. Byte 12 G.959 value from 0Ah, to 6Bh Removed P1L1-2D1, P1S1-2D2, and P1L1-2D2 from Table 5-6                                                                                                                                                                                                                                                                                                                                                                                                                            | 2014-08-28 |

| 12.1  | During the review of Rev 12.0 it was recommended that: - the contents of Table 5-3 Connector Values be moved to SFF-8024 the contents of Table 5-7 Encoding Values be returned to SFF-8024.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2014-09-12 |

| 12.2  | Further updates to clarify operation of rate select with byte content 0Eh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2014-11-21 |

| 12.3  | Added bits to support 64GFC speed negotiation Converted to SNIA template. Updated hyperlinks throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2018-07-29 |

| Rev.   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date       |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 12.4   | Replaced BR with Signaling rate and Gb/s with GBd throughout the document. Modified definition of bytes 14 and 15 in A0h, Table 4-1, to include copper cable attenuation values Added definition in Section 6.1 and 6.2.  Modified definition of bytes 56-91 in A0h, Table 4-2, to be used for enhanced features when not used for External Calibration constants. Modified Fig.4-1 to show the new allocation.  In Table 5-3 modified description for bit 1, byte 10 to refer to a secondary Fibre Channel Speed register 62. Added byte 62 to the table.  Added value 20h in byte 13, Table 5-6 for Rate Select implementation based on PMDs.  Modified name and definition of byte 19, in A0h to include cable length in base and multiplier format. Added Table 6-1.  Added a High-Power Class declaration bit 6, byte 64 in Table 8-3.  Added new value 09h in byte 94, Table 8-8 for SFF-8472, rev 12.4 compliance.  Added Section 9.6 on Additional Enhanced Features, Table 9-11 with definitions for all bytes used, Tables 9-12 (Enhanced Control Advertisement), 9-13 (Enhanced Flag Advertisement), 9-14 (Enhanced Signal Integrity Control Advertisement), 9-15 (Enhanced Control).  Modified name and definition of bit 0/byte110/A2h to clarify that this status refers to monitor data.  Added bit 4, byte 118, A2h Adaptive Input EQ Fault indicator.  Added bit 2, byte 118, A2h Enable Power Class 4.Modified definition of A2h, byte 119, bits 0,1,2,3 to be used for 50GE status.  Added advertisement bit (A2h, byte 56, bit 4) and control bit (A2h, byte 72, bit 4) for ignoring the state of the HW RS0 and RS1 pins.  Moved the RS0/1 ignore control from bit 4/ byte 72 to bit 4/ byte 73.  Added bit 4/ byte 72 Rx Output Enhanced EQ Control Override control bit.  Added Note 2 to Table 9-15 for recommended use of Tx Squelch Implementation control. | 2021-03-31 |

| 12.4.1 | Section 4.1 updated figure.  Section 4.3 added Page Description Table. Added remote transceiver pages description section.  Previously reserved bit A0h Byte 65 Bit 0; now used to indicate that other pages may exist that requires the host to perform one or multiple additional operations to determine whether a page exists.  Added bit to advertisement for Remote Performance Monitoring Registers, in A0h Byte 92 Table 8-5.  Section 12 added. Table 12-1.  Section 12.3 to Section 14 added. New material added:  - remote performance monitoring  - high accuracy timing calibration (contribution from Nikhef and CERN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2023-03-28 |

| Rev.   | Description                                                                                                                                                                                                                                                                                                                                                                                  | Date       |  |  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|--|

| 12.4.2 | Added/modify new sections 11, 12, 13 and 14.                                                                                                                                                                                                                                                                                                                                                 | 2023-05-08 |  |  |  |  |  |  |  |

|        | Added accepted comment reviews to Rev 12.4.  - A2:118.1 – added note for PL4 power level 4. (Comment Review #68)  - Section 10.4 in Rev 12.4 has been moved to Section 11 in Rev 12.5                                                                                                                                                                                                        |            |  |  |  |  |  |  |  |

|        | Two more comments from comment review needs to be addressed. When to indicate module in state 4, request is to indicate when module has reached steady state in power level 4, and not when module is entering power level 4.                                                                                                                                                                |            |  |  |  |  |  |  |  |

|        | Other comment is Page 00h / 01h are they mirror (same information) or do they relay different pages, like two pages of data.                                                                                                                                                                                                                                                                 |            |  |  |  |  |  |  |  |

|        | Applied new text to previous document Rev 12.4 Section 10.4, clarifying Pg 00h/01h, per meeting on 2023-05-06 discussion. This will be in Section 11.1 in this revision.                                                                                                                                                                                                                     |            |  |  |  |  |  |  |  |

|        | <ul> <li>Changes to 12.4.1 after review, Section 13.</li> <li>Change nsec to ns, atto-seconds to appropriately scaled fs (femto-seconds)</li> <li>Remove "Magic Number" replace with Format ID in section 13.</li> <li>Change 0xABCD to ABCDh. (Editorial)</li> <li>Updated section 13 for consistency, clarification.</li> <li>Added description of Calibration Loopback Module.</li> </ul> |            |  |  |  |  |  |  |  |

|        | Added Appendix Section 14 to supplement Section 12.                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |  |  |

| 12.4.3 | Update from comment reviews (about 140 comments).  Changed Section 2 and 3 per comment review to copy from SFF-8636. Added Glossary, Definitions                                                                                                                                                                                                                                             | 2025-03-04 |  |  |  |  |  |  |  |

|        | Per comment review remote section 14 and moved to Section 12.4.                                                                                                                                                                                                                                                                                                                              |            |  |  |  |  |  |  |  |

|        | Section 13 High Accuracy Timing and Tight-Sync merge. Newer definition of memory map compared to draft revision 12.4.2.                                                                                                                                                                                                                                                                      |            |  |  |  |  |  |  |  |

| ents |

|------|

|      |

| 2                                                                          | 1 | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                                   |

|----------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 3<br>4<br>5<br>6                                                           | 2 | References and Conventions 2.1 Industry Documents 2.2 Sources 2.3 Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11<br>11<br>11<br>12                                                 |

| 7<br>8<br>9<br>10                                                          | 3 | Keywords, Acronyms and Definitions 3.1 Keywords 3.2 Acronyms and Abbrevations 3.3 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13<br>13<br>14<br>15                                                 |

| 11<br>12<br>13<br>14<br>15<br>16                                           | 4 | Memory Organization 4.1 Introduction 4.2 2-wire Interface Fields 4.3 Pages 4.3.1 Remote Transceiver Pages 4.4 Data Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16<br>16<br>16<br>17<br>17                                           |

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26                   | 5 | Identifiers and Codes 5.1 Physical Device Identifier Values [Address A0h, Byte 0] 5.2 Physical Device Extended Identifier Values [Address A0h, Byte 1] 5.3 Connector Values [Address A0h, Byte 2] 5.4 Transceiver Compliance Codes [Address A0h, Bytes 3 to 10, 36 and 62] 5.4.1 SONET Reach Specifier Bits [Address A0h, Byte 4, bits 3-4] 5.4.2 Examples of Transceiver Compliance Codes [Address A0h, Bytes 3-10] 5.5 Encoding [Address A0h, Byte 11] 5.6 Signaling rate, nominal [Address A0h, Byte 12] 5.7 Rate Identifier [Address A0h, Byte 13]                             | 21<br>21<br>22<br>22<br>22<br>24<br>25<br>26<br>26<br>27             |

| 27<br>28<br>29<br>30<br>31<br>32<br>33                                     | 6 | Link Length 6.1 Length (single mode, km) or Copper Cable Attenuation [Address A0h, Byte 14] 6.2 Length (single mode, 100s m) or Copper Cable Attenuation [Address A0h, Byte 15] 6.3 Length (50 um, OM2) [Address A0h, Byte 16] 6.4 Length (62.5 um, OM1) [Address A0h, Byte 17] 6.5 Length (50 um, OM4) and Length (Active Cable or Copper) [Address A0h, Byte 18] 6.6 Length (50 um, OM3) and Length (Active Cable or Copper), additional [Address A0h, Byte 19]                                                                                                                  | 28<br>28<br>28<br>28<br>28<br>28<br>28                               |

| 34<br>35<br>36<br>37<br>38                                                 | 7 | Vendor Fields 7.1 Vendor name [Address A0h, Bytes 20-35] 7.2 Vendor OUI [Address A0h, Bytes 37-39] 7.3 Vendor PN [Address A0h, Bytes 40-55] 7.4 Vendor Rev [Address A0h, Bytes 56-59]                                                                                                                                                                                                                                                                                                                                                                                              | 29<br>29<br>29<br>29                                                 |

| 39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51 | 8 | Link Characteristics 8.1 Optical and Cable Variants Specification Compliance [Address A0h, Bytes 60-61] 8.2 CC_BASE [Address A0h, Byte 63] 8.3 Option Values [Address A0h, Bytes 64-65] 8.4 Signaling Rate, max [Address A0h, Byte 66] 8.5 Signaling Rate, min [Address A0h, Byte 67] 8.6 Vendor SN [Address A0h, Bytes 68-83] 8.7 Date Code [Address A0h, Bytes 84-91] 8.8 Diagnostic Monitoring Type [Address A0h, Byte 92] 8.9 Addressing Modes 8.10 Enhanced Options [Address A0h, Byte 93] 8.11 SFF-8472 Compliance [Address A0h, Byte 94] 8.12 CC_EXT [Address A0h, Byte 95] | 30<br>30<br>30<br>31<br>31<br>32<br>32<br>32<br>32<br>33<br>33<br>35 |

| 52<br>53                                                                   | 9 | Diagnostics<br>9.1 Overview [Address A2h]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35<br>35                                                             |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                                                                                                         |    | Internal Calibration External Calibration Alarm and Warning Thresholds [Address A2h, Bytes 0-39] Calibration Constants for External Calibration Option [Address A2h, Bytes 56-91] Additional Enhanced Features CC_DMI [Address A2h, Byte 95] Real Time Diagnostic and Control Registers [Address A2h, Bytes 96-111] Alarm and Warning Flag Bits [Address A2h, Bytes 112-117]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36<br>38<br>39<br>41<br>43<br>46<br>47<br>48                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 9<br>10<br>11<br>12                                                                                                                          | 10 | Extended Information  10.1 Extended Module Control/Status Bytes [Address A2h, Bytes 118-119]  10.2 Vendor Specific Locations [Address A2h, Bytes 120-126]  10.3 Optional Page Select Byte [Address A2h, Byte 127]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50<br>50<br>51<br>51                                                                                                 |

| 13<br>14<br>15                                                                                                                               | 11 | Address 02h Page 00h/01h 11.1 User Accessible EEPROM Locations [Address A2h, Page 00h / 01h, Bytes 128-247] 11.2 Vendor Specific Control Function Locations [Address A2h, Page 00h / 01h, Bytes 248-255]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52<br>52<br>52                                                                                                       |

| 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39 | 12 | Address A2h Page 02h Tunability and RPM  12.1.1 Feature Advertisement  12.2 Variable Receiver Decision Threshold Control [A2h, Page 02h, Bytes 130-131]  12.2.1 RDT Behavior prior to and including Rev 12.4  12.2.2 RDT Behavior post Rev 12.4  12.3 Remote Performance Monitoring (RPM)  12.3.1 Remote Performance Registers  12.3.2 Remote Performance Latched Alarms  12.3.3 Remote Performance Monitoring Status  12.3.4 Remote Performance Monitoring Error Counters  12.3.5 Remote Performance Monitoring Remote Control Messages  12.3.6 RPM Tx Rx Enable and Tx Modulation Index  12.3.6.1 Dynamic Adjustment of modulation index  12.3.7 RPM Enable/Disable  12.3.8 RPM Data Transmission Control A2h Page 02 Bytes 214-215  12.3.9 RPM Control and Configuration A2h Page 02 Bytes 216-219  12.3.10 Transmitting and Receiving User Data over Remote PM channel.  12.4 TOM (Type Of Message) Summary  12.4.1 TOM: 2A0h. CTRL_CMD / RSP message  12.4.1.1 TOM 2A0h. msgType = 0b  12.4.2 TOM: 2A8h/02A9h. Sending Page Data  12.4.3 TOM: 2A8h. Extended Idle  12.4.1 TOM: 2A8h. Security Idle | 53<br>53<br>54<br>54<br>56<br>56<br>57<br>59<br>60<br>61<br>61<br>62<br>63<br>64<br>66<br>66<br>67<br>67<br>68<br>69 |

| 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>57                                     | 13 | Address A2h Page 03h High Accuracy Timing Format ID (Bytes 128-129) CC_CALIB (Byte 255) 13.1 Definition of time reference planes and delays associated 13.1.1 Delays associated to Optical Modules 13.1.2 Delays associated to Loopback Modules 13.2 Numeric Formats 13.2.1 Description of the q16.16 format for time representation 13.2.2 Description of the q8.16 format for time correction 13.2.3 Description of the q8.8 format for temperature 13.2.4 Description of the q8.8 format for wavelength correction 13.3.1 Version (Byte 130) 13.3.2 Calibration Date (Bytes 131-133) 13.3.3 Calibration Unique Identifier (CUI) (Bytes 134-139) 13.3.4 Calibration format for Optical Modules (Bytes 150-254) 13.4.1 Nb_Lanes (Byte 150)                                                                                                                                                                                                                                                                                                                                                             | 70<br>70<br>70<br>71<br>71<br>72<br>72<br>72<br>72<br>73<br>73<br>73<br>74<br>74                                     |

| 1  | 13.4.2 Op_Mode_Id (Byte 151)                                            | 74 |

|----|-------------------------------------------------------------------------|----|

| 2  | 13.4.3 RX Power Dependent Delay (Bytes 152-166)                         | 74 |

| 3  | 13.4.4 T_Detune_Offset (Bytes 167-168), T_Detune_Slope (Bytes 169-170)  | 75 |

| 4  | 13.4.5 Delta_Rx_max (Bytes 171-174), Delta_Tx_Max (Bytes 175-178)       | 75 |

| 5  | 13.4.6 Avg_Rx_LaneN with N=0 for SFF8472 (Bytes (179-182)+N*8)          | 75 |

| 6  | 13.4.7 Avg_Tx_LaneN with N=0 for SFF8472 (Bytes (183-186)+N*8)          | 75 |

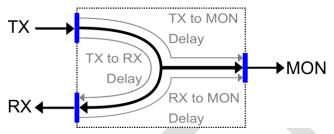

| 7  | 13.5 Calibration format for Loopback Modules (Bytes 150-254)            | 76 |

| 8  | 13.5.1 Calibration Inaccuracy (Bytes 150-153)                           | 76 |

| 9  | TX to RX Delay (Bytes 155-158)                                          | 76 |

| 10 | 13.5.2 76                                                               |    |

| 11 | TX to MON Delay (Bytes 160-163)                                         | 76 |

| 12 | 13.5.3 76                                                               |    |

| 13 | 13.5.4 RX to MON Delay (Bytes 165-168)                                  | 76 |

| 14 |                                                                         |    |

| 15 | Figures                                                                 |    |

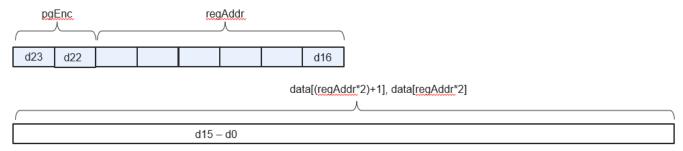

| 16 | Figure 3-1 Bit Organization                                             | 15 |

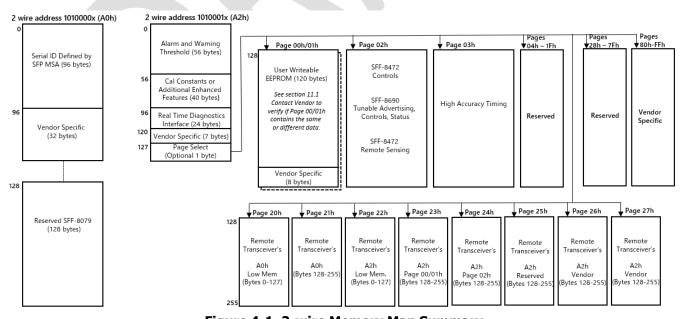

| 17 | Figure 4-1 2-wire Memory Map Summary                                    | 16 |

| 18 | Figure 12-1 G.698.4 Frame Structure                                     | 56 |

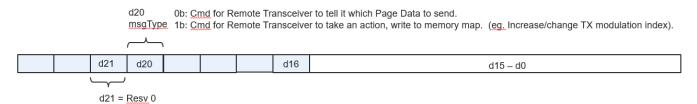

| 19 | Figure 12-2 TOM 2A0h Generic Message                                    | 66 |

| 20 | Figure 12-3 TOM 2A0h msgType 0b fields                                  | 67 |

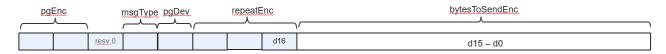

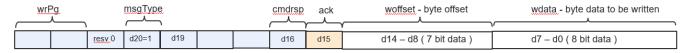

| 21 | Figure 12-4 TOM 2A0h msgType 1b fields                                  | 68 |

| 22 | Figure 12-5 TOM 2A8h/2A9h fields                                        | 69 |

| 23 | Figure 12-6 TOM 2AAh Extended Idle Fields                               | 69 |

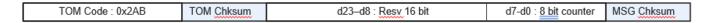

| 24 | Figure 12-7 TOM 2ABh Security Idle Fields                               | 69 |

| 25 | Figure 13-1 Calibration Loopback Module                                 | 76 |

| 26 |                                                                         |    |

| 27 | Tables                                                                  |    |

| 28 |                                                                         |    |

| 29 | Table 4-1 Page Description                                              | 17 |

| 30 | Table 4-2 Data Fields - Address A0h                                     | 18 |

| 31 | Table 4-3 Data Fields - Address A2h                                     | 19 |

| 32 | Table 4-4 Data Fields - Address A2h Page Tables                         | 19 |

| 33 | Table 4-5 Transceiver Identification/Performance Examples               | 20 |

| 34 | Table 4-6 Copper Cable Identification/Performance Examples              | 21 |

| 35 | Table 5-1 Physical Device Identifier Values                             | 21 |

| 36 | Table 5-2 Physical Device Extended Identifier Values                    | 22 |

| 37 | Table 5-3 Transceiver Compliance Codes                                  | 23 |

| 38 | Table 5-4 SONET Reach Specifier Bits                                    | 24 |

| 39 | Table 5-5 Transceiver Identification Examples                           | 25 |

| 40 | Table 5-6 Rate Identifier                                               | 27 |

| 41 | Table 6-1 Cable Length, Additional                                      | 29 |

| 42 | Table 8-1 Passive Cable Specification Compliance (A0h Byte 8 Bit 2 set) | 30 |

| 43 | Table 8-2 Active Cable Specification Compliance (A0h Byte 8 Bit 3 set)  | 30 |

| 44 | Table 8-3 Option Values                                                 | 31 |

| 45 | Table 8-4 Date Code                                                     | 32 |

| 46 | Table 8-5 Diagnostic Monitoring Type                                    | 33 |

| 47 | Table 8-6 Enhanced Options                                              | 34 |

| 48 | Table 8-7 I/O Timing for Soft Control and Status Functions              | 34 |

| 49 | Table 8-8 SFF-8472 Compliance                                           | 35 |

| 50 | Table 9-1 Bit Weights (Degrees C) for Temperature Reporting Registers   | 37 |

| 51 | Table 9-2 Digital Temperature Format                                    | 37 |

| 52 | Table 9-3 Bit Weights (mA) for TEC current Reporting Registers          | 37 |

| 53 | Table 9-4 TEC Current Format                                            | 37 |

| 54 | Table 9-5 Alarm and Warning Thresholds                                  | 39 |

| 55 | Table 9-6 Calibration Constants for External Calibration Option         | 41 |

| 56 | Table 9-7 Unsigned Fixed-Point Binary Format for Slopes                 | 42 |

| 57 | Table 9-8 Format for Offsets                                            | 42 |

| 58 | Table 9-9 IEEE Std 754 Single-Precision Floating Point Number Format    | 42 |

| 59 | Table 9-10 Example of Floating Point Representation                     | 43 |

**DRAFT** SFF-8472 Rev 12.4.3 Table 9-11 Additional Enhanced Features Table 9-12 Enhanced Control Advertisement Table 9-13 Enhanced Flags Advertisement Table 9-14 Enhanced Signal Integrity Control Advertisement Table 9-15 Enhanced Control Table 9-16 A/D Values and Status Bits Table 9-17 Alarm and Warning Flag Bits Table 9-18 Input Equalization (Address A2h Byte 114) Table 9-19 Output Emphasis Control (Address A2h Byte 115) Table 10-1 Extended Module Control/Status Bytes Table 10-2 Retimer/CDR Rate Select Logic Table Table 10-3 Optional Page Select Byte Table 11-1 User Accessible EEPROM Locations Table 11-2 Vendor Specific Control Function Locations Table 12-1 Register Groups for Page 02h Table 12-2 Page 02h Feature Advertisement Table 12-3 Variable Receiver Decision Threshold Control Table 12-4 Register Summary for Remote Performance Monitoring Table 12-5 Page 02h Remote Performance COR Latched Alarms Table 12-6 Page 02h Remote Performance Monitoring Status Registers Table 12-7 Page 02h Remote Performance Monitoring Error Counters Table 12-8 Page 02h Remote Performance Monitoring Remote Control Message Table 12-9 Page 02h Remote Performance Monitoring Tx Modulation Index Table 12-10 RPM Control Registers Table 12-11 RPM Data Transmission Control Registers Table 12-12 RPM TX Security Features Table 12-13 RPM RX Security Features Table 12-14 Page 02h RemotePM TX RX User Data Table 12-15 Page 02h RemotePM TX RX User Data Table 13-1 Register Summary Page 03h – Calibration format for Optical Modules Table 13-2 Register Summary Page 03h - Calibration format for Loopback Modules Table 13-3 Register Groups for Page 03h Table 13-4 Page 03h High Accuracy Timing Calibration Date Encoding Table 13-5 Page 03h Calibrated Unique ID format

# 1 Scope

This document defines a memory map and digital management interface for monitoring and control of SFP+ optical transceivers and similar modules.

The interface is an extension of the 2-wire interface ID interface defined in the GBIC specification as well as the SFP MSA. Both specifications define a 256 byte memory map which is accessible over a 2-wire serial interface at the 8 bit address 1010000X (A0h). The enhanced digital management interface makes use of the 8 bit address 1010001X (A2h), so the originally defined 2-wire interface ID memory map remains unchanged. The interface is backward compatible with both the GBIC specification and the SFP MSA.

In order to provide memory space for future extensions, multiple optional pages are defined for the upper 128 bytes of the A2h memory space.

# 2 References and Conventions

# 2.1 Industry Documents

The following documents are relevant to this specification:

| . • |                      |                                                                            |

|-----|----------------------|----------------------------------------------------------------------------|

| 20  | INF-8074             | SFP (Small Formfactor Pluggable) 1 Gb/s Transceiver                        |

| 21  | SFF-8024             | SFF Module Management Reference Code Tables                                |

| 22  | SFF-8053             | GBIC (Gigabit Interface Converter)                                         |

| 23  | SFF-8079             | SFP Rate and Application Selection                                         |

| 24  | SFF-8089             | SFP Rate and Application Codes                                             |

| 25  | SFF-8418             | SFP+ 10 Gb/s Electrical Interface                                          |

| 26  | SFF-8419             | SFP+ Power and Low Speed Interface                                         |

| 27  | SFF-8431             | SFP+ 10 Gb/s and Low Speed Electrical Interface                            |

| 28  | SFF-8690             | Tunable SFP+ Memory Map                                                    |

| 29  | INCITS FC-PI-4/5/6/7 | Fibre Channel Physical Interface 4/5/6/7                                   |

| 30  | IEEE Std 754         | Standard for Floating-Point Arithmetic                                     |

| 31  | IEEE Std 802.3       | IEEE Standard for Ethernet                                                 |

| 32  | IEEE Std 1588        | IEEE Standard for a Precision Clock Synchronization Protocol for Networked |

| 33  |                      | Measurement and Control Systems                                            |

| 34  | MOPA                 | Mobile Optical Pluggable Alliance.                                         |

| 35  |                      | "MOPA Remote Monitoring Specifications v1.0"                               |

| 36  |                      | https://mopa-alliance.org/papers-and-presentations/                        |

| 37  | ITU-T G.698.4        | Multichannel bi-directional DWDM applications with port agnostics          |

| 38  |                      | single-channel optical interfaces.                                         |

|     |                      |                                                                            |

H. Peek and P. Jansweijer, "White Rabbit Absolute Calibration", 2018 IEEE International Symposium on Precision Clock Synchronization for Measurement, Control, and Communication (ISPCS), Geneva, Switzerland, 2018, pp. 1-5, doi: 10.1109/ISPCS.2018.8543067. https://ieeexplore.ieee.org/document/8543067

## 2.2 Sources

The complete list of SFF documents which have been published are currently being worked on, or that have been expired by the SFF Committee can be found at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Suggestions for improvement of this specification are welcome and should be submitted to <a href="https://www.snia.org/feedback">https://www.snia.org/feedback</a>.

# 7

8 9

# 10 11 12 13 14 15

#### 2.3 **Conventions**

The following conventions are used throughout this document:

**DEFINITIONS**: Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

ORDER OF PRECEDENCE: If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

NUMBERING CONVENTIONS: The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1.323.462.9 | 1 323 462.9 | 1 323 462.9 |

NUMERALS CONSTANTS: Numerals without suffix are understood as numbers in decimal notation (e.g. 16). Hexadecimal literals are marked with a suffix 'h' (e.g. 10h), often written with leading zeroes (0010h). Binary literals are marked with a suffix 'b' (e.g. 10000b), often written with leading zeroes (00010000b). The suffixes may be omitted for unambiguous cases like 0=0b=0h and 1=1b=1h. Spaces may be inserted to make long hexadecimal or binary digit strings readable (e.g. 0001 0000b).

# 3 Keywords, Acronyms and Definitions

For the purposes of this document, the following keywords, acronyms, and definitions apply.

3.1 Keywords

May: Indicates flexibility of choice with no implied preference.

May or may not: Indicates flexibility of choice with no implied preference.

**Obsolete:** Indicates that an item was defined in prior specifications but has been removed from this specification.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be done in the same way as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Prohibited:** Describes a feature, function, or coded value that is defined in a referenced specification to which this SFF specification makes a reference, where the use of said feature, function, or coded value is not allowed for implementations of this specification.

**Reserved:** Defines the signal on a connector contact [when] its actual function is set aside for future standardization. It is not available for vendor-specific use. Where this term is used for bits, bytes, fields, and values; the bits, bytes, fields, and values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Restricted:** Refers to features, bits, bytes, words, and fields that are set aside for other standardization purposes (e.g., entities). If the context of the specification applies the restricted designation, then the restricted bit, byte, word, or field shall be treated as a value whose definition is not in scope of this document, and is not interpreted by this specification.

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

#### 3.2 **Acronyms and Abbrevations**

3 В binary (suffix to preceding binary based number) ٥С

4 degrees Celsius (thermal unit associated with a value)

5 CDR clock and data recovery

6 COR Clear On Read.

1 2

7 decibel (base 10 logarithmic unit) dB 8 decibels above one milliwatt dBm **Digital Diagnostics Monitoring** 9 DDM

gigabits per second (i.e., 10<sup>9</sup> bits per second) Gbps 10

gigahertz (i.e., 10<sup>9</sup> cycles per second) 11 GHz

12 h hexadecimal (suffix to preceding hexadecimal based number)

Head End Equipment 13 HEE

14 hertz (i.e., cycles per second) Hz

15 kHz kilohertz (i.e., 10<sup>3</sup> cycles per second)

kilometer (i.e., 10<sup>3</sup> meters) 16 km

17 LSB least significant bit meter (unit of length) 18 m

milliampere (i.e., 10^-3 amperes) 19 mΑ

megabits per second (i.e., 10<sup>6</sup> bits per second) 20 Mbps

megahertz (i.e., 10<sup>6</sup> cycles per second) MHz 21

millisecond (i.e., 10^-3 seconds) 22 ms

23 **MSB** most significant bit 24 millivolt (i.e., 10^-3 volts) m۷ 25 mW milliwatt (i.e., 10^-3 watts) nanometer (i.e., 10^-9 meters) 26 nm nanosecond (i.e., 10^-9 seconds) 27 ns

28 P-P peak-to-peak

picosecond (i.e., 10^-12 seconds) 29 ps 30 **RDDM** Remote Digital Diagnostics Monitoring

31 Rx receiver

32 second (unit of time) s

33 TC temperature controller (e.g. thermo-electric cooler)

34 TEE Tail End Equipment

35 transmitter Tx

microampere (i.e., 10^-6 amperes) 36 μA 37 micrometer (i.e., 10^-6 meters) μm microsecond (i.e., 10^-6 seconds) 38 μs microvolt (i.e., 10^-6 volts) 39 μV

microwatt (i.e., 10^-6 watts) 40 μW volt (unit of electrical potential) 41 W watt (unit of electrical power) 42

43 44

# 3.3

# Bit Organization

**Definitions**

8-bit fields have the most significant bit at bit 7, and 16-bit fields have the most significant bit at bit 15. See Figure 3-1.

5 6

| MSI |    |    |    |    |    | MSB  |          | 8 | -bit Fie | ld |   | LS | В |     |   |

|-----|----|----|----|----|----|------|----------|---|----------|----|---|----|---|-----|---|

| MSB |    |    |    |    |    | 16-b | it Field |   |          |    |   |    |   | LSB |   |

| 15  | 14 | 13 | 12 | 11 | 10 | 9    | 8        | 7 | 6        | 5  | 4 | 3  | 2 | 1   | 0 |

Figure 3-1 Bit Organization

8 9 10

11

12

13 14

7

# **Big Endian**

The default byte order of multi-byte registers representing numerical types is Big Endian, that is the lowest byte address contains the most significant byte of the multi-byte value.

# 4 Memory Organization

## 4.1 Introduction

The enhanced digital diagnostic interface is a superset of the MOD\_DEF interface defined in the SFP MSA document dated September 14, 2000, later submitted to the SFF Committee as INF-8074. The 2-wire interface pin definitions, hardware, and timing was initially defined there. SFF-8431, later superseded by SFF-8419 define the low speed electrical and management interface specifications for SFP+. Pluggable modules such as SFP+, SFP28 and future SFP form factor that are compliant to SFF-8431 and SFF-8419 hereafter referred to as SFP+ may use this management interface.

This document describes an extension to the memory map defined in the SFP MSA (see Figure 4-1). The enhanced interface uses the 2-wire serial bus address 1010001X, commonly referred to as A2h, and where X can be 1 for a read operation or 0 for a write operation. Reads from this address provide diagnostic information about the module's present operating conditions. The transceiver generates this diagnostic data by digitization of internal analog signals. Calibration and alarm/warning threshold data is written during device manufacture.

All bits that are reserved for SFF-8472 shall be set to zero and/or ignored.

Bits labeled as reserved or optional for other usage, such as for SFF-8079, shall be implemented per such other documents, or set to zero and/or ignored if not implemented.

If optional features for SFF-8472 are implemented, they shall be implemented as defined in SFF-8472. If they are not implemented or not applicable to the device, then write bits shall be ignored, and status bits shall be set to zero.

Additional A0h and A2h memory allocations were provided in revision 9.5 to support multi-rate and application selection as defined in the SFF-8079 and SFF-8089 specifications.

Various extensions have been made in revisions since revision 10.4. These include adding new connectors, industry form factors, transceiver codes and controls for transceiver features.

# 4.2 2-wire Interface Fields

Figure 4-1 2-wire Memory Map Summary

The optional Page Select byte expands the range of information that can be provided by the manufacturer. Where used in this specification the Page ID is defined in hexadecimal. Note: Vendor Specific Page IDs may be password-

The use of Paging System is Optional, and when used the pages shall be used as described in the following table.

In this revision, see Table 8-3, A0h.Byte65.Bit0, which was previously reserved in SFF-8472 Rev 12.4, is now used

to indicate that there are additional pages. If this bit is 0b, then the transceiver module has only legacy pages 00/01

and 02h. If this bit is 1b, there are one or more additional pages to be discovered. To discover if a page is supported,

the host writes A2h.Byte127 (Page Select) byte, wait momentarily until the page change is complete and then read-

1

2 3 4

5

4.3

**Pages**

6 7

8 9 10

19 20

back the page select byte. If the page is supported then the page select byte will return what is being written, otherwise it will return 00h. Once the page has been selected, there may need to be additional validations that needs to be performed with the page, for example for Page 03h, the first 2 bytes, byte 128-129 are format ID as well as the last byte being CC\_CALIB, a checksum. This is to ensure that modules that are non-compliant to the additional page description are appropriately managed.

protected. The location of the password is not defined in SFF-8472 and will be defined by the vendor.

**Table 4-1 Page Description**

| Page    | Description of Pages                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------|

| 00h     | Contains the legacy unpaged upper memory of A2h.                                                                  |

| 01h     | Both Page 00h and 01h are defined to point to the same information for backward compatibility.                    |

| 02h     | Page used to implement Tunability as per SFF-8690. Page used for RXDTV control and Remote Performance Monitoring. |

| 03h     | High Accuracy Timing Calibrations                                                                                 |

| 04h-1Fh | Reserved                                                                                                          |

| 20h     | Remote Transceiver SFF-8472 A0h Bytes 0 – 127                                                                     |

| 21h     | Remote Transceiver SFF-8472 A0h Bytes 128 - 255                                                                   |

| 22h     | Remote Transceiver SFF-8472 A2h Bytes 0-127                                                                       |

| 23h     | Remote Transceiver SFF-8472 A2h Page 00h/01h Bytes 128-255                                                        |