# SFF-TA-1009

Specification for

# **Enterprise and Datacenter Standard Form Factor Pin and**

# Signal Specification

Rev 4.0<u>.1</u>

January 6, 2025 May 3, 2024

SECRETARIAT: SFF TA TWG

This specification is made available for public review at <u>https://www.snia.org/sff/specifications</u>. Comments may be submitted at <u>https://www.snia.org/feedback</u>. Comments received will be considered for inclusion in future revisions of this specification.

This specification provides a common reference for host systems manufacturers, host system integrators, and device suppliers. This specification originates from Enterprise and Datacenter SSD Form Factor Working Group (EDSFF). With non-SSD devices also using EDSFF and agreement from the EDSFF Working Group, the SFF TA TWG changed EDSFF to Enterprise and Datacenter Standard Form Factor.

This document has been released by SNIA. The SFF TWG believes that the ideas, methodologies, and technologies described in this document are technically accurate and are appropriate for widespread distribution.

The description of the details in this specification does not assure that the specific component is available from device suppliers. If such a device is supplied, then it shall comply with this specification to achieve interoperability between device suppliers.

ABSTRACT: This specification defines the pin list and pin placement, function of the pins, device specific electrical requirements, and specific features of enterprise and datacenter-based devices. This specification relies on SFF-TA-1002 for the connector mechanicals and SFF-TA-1006, SFF-TA-1007, and SFF-TA-1008 form factor specifications for the form factor mechanicals.

POINTS OF CONTACT: <u>SNIA Technical Council Managing Director Anthony Constantine</u> Chairman SFF TA TWG <u>Email: TCMD@snia.org Intel Corporation</u> <u>Chair@snia.org</u> <u>-2111 NE 25th Ave,</u>

#### PublishedDRAFT

EDITORS: Anthony Constantine, Micron Technology -MS JF5-270 -Hillsboro, OR 97124 -Ph: 971 215 1128 -Email: <u>anthony.m.constantine@intel.com</u>

#### Intellectual Property

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is considered SNIA Architecture and is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published.

The SNIA IP Review Process is still in progress. If IP disclosures that affect this specification are made during this process, this specification may be withdrawn.

Additional information can be found at the following locations:

- Results of IP Disclosures: <u>https://www.snia.org/sffdisclosures</u>

- SNIA IP Policy: <u>https://www.snia.org/ippolicy</u>

#### Copyright

The SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <u>copyright request@snia.org</u>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

#### Disclaimer

The information contained in this publication is subject to change without notice. The SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to <u>https://www.snia.org/feedback/</u>.

#### Foreword

The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, as well as since SFF's transition to SNIA in 2016, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at <u>https://www.snia.org/sff/join</u>.

#### **Revision History**

| Rev | 1.0 | March 23, 2018:                                                                                                                                                                                          |

|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     | - Initial release                                                                                                                                                                                        |

| Rev | 2.0 | May 22, 2018:                                                                                                                                                                                            |

|     |     | - Change to TX/RX ordering and changed table orientation for tables 4-4, 4-5, and 4-6.                                                                                                                   |

|     |     | - Clarification to power sequencing requirements (section 5.2).                                                                                                                                          |

|     |     | - Update to unused reference clock guidance (section 4.2.2).                                                                                                                                             |

|     |     | <ul> <li>Minor editorial and formatting changes throughout document.</li> </ul>                                                                                                                          |

| Rev | 3.0 | March 19, 2021:                                                                                                                                                                                          |

|     |     | <ul> <li>Name change to Enterprise and Datacenter Standard Form Factor</li> </ul>                                                                                                                        |

|     |     | - Revised to new format used in SFF                                                                                                                                                                      |

|     |     | - Updated Revision of reference documents                                                                                                                                                                |

|     |     | - Editorial cleanup throughout document                                                                                                                                                                  |

|     |     | <ul> <li>Minor clarifications made throughout document</li> </ul>                                                                                                                                        |

|     |     | - Power and Grounds: Additional requirements and expectations added to power sequencing                                                                                                                  |

|     |     | <ul> <li>PCIe signals: Clarifications made to PCIe single port mode below x4</li> </ul>                                                                                                                  |

|     |     | - CLKREQ: Clarifications made to CLKREQ# and PERST1# behavior in relation to DUALPORTEN#                                                                                                                 |

|     |     | - Addition of Pull-up/Pull-down locations and values to signals requiring Pull-up/Pull-down                                                                                                              |

|     |     | - SMBus: Clarification on device and host pull-ups                                                                                                                                                       |

|     |     | - SMRST#: Clarifications made to SMRST behavior                                                                                                                                                          |

|     |     | - DUALPORTEN#: Replaced table on dual port vs. single port usage with simpler definition                                                                                                                 |

|     |     | - LED/ACTIVITY: ACTIVITY portion removed. Spec will no longer support the use of ACTIVITY                                                                                                                |

|     |     | - Errata fix in tables 4-4, 4-5, and 4-6 to rename LED#/Activity to LED to match functional definition along with title of these tables. Changed 3.3 VAux to 3.3 Vaux                                    |

|     |     | <ul> <li>12V supply requirements: Added new requirements for Max sustained power, Initial power,<br/>max power, and slew rate</li> </ul>                                                                 |

|     |     | - 3.3 Vaux supply requirements: Clarified measurement time for current.                                                                                                                                  |

|     |     | <ul> <li>Timing requirements: Added specs for SMRST#, PWRDIS de-assertion time and PERST to 12V<br/>power</li> </ul>                                                                                     |

|     |     | - 3.3V Logic signaling: Added SMBus to signals covered and its operating voltage, a new Vil for                                                                                                          |

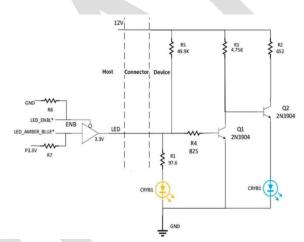

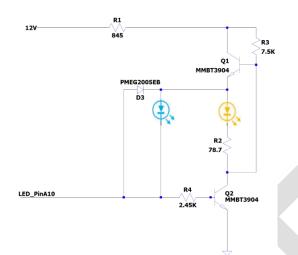

|     |     | LEDs, updated leakage currents, and added notes.<br>- Added Amber/Blue LED for SFF-TA-1008 along with description, values, and example                                                                   |

|     |     | schematics                                                                                                                                                                                               |

|     |     | - LED Requirements: relaxed wavelength and point intensity ranges                                                                                                                                        |

|     |     | <ul> <li>Clarified Amber LED usage for SFF-TA-1006 and SFF-TA-1007</li> </ul>                                                                                                                            |

|     |     | <ul> <li>Section 8 added for Electrical Requirements including S-parameters and eye masks</li> </ul>                                                                                                     |

| Rev | 3.1 | January 6, 2023:                                                                                                                                                                                         |

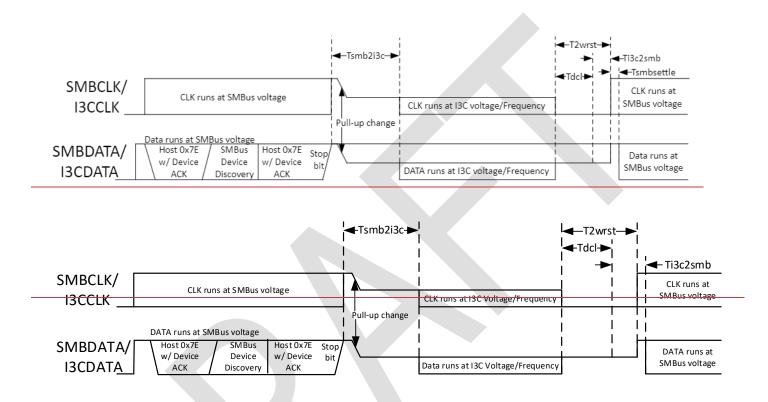

|     | 012 | - Added I3C Basic signal requirements, voltage details, and transition timings.                                                                                                                          |

|     |     | - Added I3CCLK/I3CDATA to pin list, pin description and shared places with SMBCLK/SMBDATA                                                                                                                |

|     |     | - Changed name of SMBRST# to SMRST#                                                                                                                                                                      |

|     |     | - Added NIC signals to pin list for support of a 4C+ pin out.                                                                                                                                            |

|     |     | - Added NIC_DETECT signal, modified RSVD and MFG definitions for 4C+ usage.                                                                                                                              |

|     |     | - Added 4C+ pin out.                                                                                                                                                                                     |

|     |     | <ul> <li>Added clarification on LED behavior for activity behavior and PWRDIS for the amber/blue LED</li> <li>Added informative section on I3C basic implementation including transition flow</li> </ul> |

|     |     |                                                                                                                                                                                                          |

Enterprise and Datacenter Standard Form Factor Pin and Signal Specification

Copyright © 20252024 SNIA. All rights reserved.

Page 4

- Added informative NIC implementation section including signal definitions and other notes. Clarified usage where pins are muxed with non 4C+ signals.

#### Rev 4.0

- Added USB 2.0 signals into pin list and NIC signals description

- Clarification on SMBus/I3C Basic state during power cycle

- Comments added for 12Vtol and 12Vpinit in Table 6-1

- Clarification to notes in Table 6-3

- Addition of ILED minimum current in Table 6-4

- Addition of White LED to Section 7

- Added PCIe 6.0 electrical requirements into Section 8 and updated reference to 6.0.

- Added pointers to PCI-SIG ECN for I3C Basic and comment for Tsmb2i3c relation to pull-up

- Editorial cleanup throughout document

#### **Rev 4.0.1** January 6, 2025:

May 3, 2024:

- Boiler plate language changes.

- Corrected SMBus initiator to controller and host/device to controller/target in section 5.3.2

- Errata changes and clarifications to I3C timings in Section 6.4.

- Fixed reference in Section 7.2.1

- Clarified wording around I3C Basic in Section 10

### Contents

| 1. | Scope<br>1.1 Application Specific Criteria                                                                                                                                                                                                                                                                                                                                                                                                    | <u>9</u> 8<br><u>9</u> 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | References and Conventions2.1Industry Documents2.2Sources2.3Conventions                                                                                                                                                                                                                                                                                                                                                                       | <u>98</u><br><u>98</u><br><u>98</u><br><u>10</u> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3. | Keywords, Acronyms, and Definitions3.1Keywords3.2Acronyms and Abbreviations3.3Definitions                                                                                                                                                                                                                                                                                                                                                     | <u>1140</u><br><u>11</u> 40<br><u>11</u> 40<br><u>11</u> 40<br><u>12</u> 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4. | General Description                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>13<del>12</del></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5. | Signal List<br>5.1 Power and Grounds<br>5.2 PCIe Signals<br>5.2.1 High Speed Signals (PERp/n, PETp/n)<br>5.2.2 Reference Clock<br>5.2.3 PERST#<br>5.2.4 CLKREQ#<br>5.3 Sideband Signals<br>5.3.1 PRSNT[02]#<br>5.3.2 SMBus Interface<br>5.3.3 I3C Basic Interface<br>5.3.4 SMRST#<br>5.3.5 DUALPORTEN#<br>5.3.6 LED<br>5.3.7 PWRDIS<br>5.3.8 MFG<br>5.3.9 RFU<br>5.4 NIC Signals<br>5.4.1 GND/NIC_DETECT#<br>5.5 Connector pinout definitions | $\frac{1413}{1615} \\ \frac{1716}{1716} \\ \frac{1716}{1817} \\ \frac{1918}{1918} \\ \frac{1918}{1918} \\ \frac{1918}{2019} \\ \frac{2019}{2019} \\ \frac{2019}{2019} \\ \frac{2019}{2019} \\ \frac{2019}{2120} \\ \frac{2120}{2120} \\ \frac{2120}{2120$ |

| 6. | Electrical Requirements6.1Power Supply Requirements6.2Timings6.33.3 V Logic Signal Requirements6.4I3C Basic Signal Requirements                                                                                                                                                                                                                                                                                                               | <u>30</u> 29<br><u>30</u> 29<br><u>31</u> 30<br><u>31</u> 30<br><u>31</u> 30<br><u>32</u> 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7. | LEDs<br>7.1 Location 1 LED(s)<br>7.1.1 Green LED (Class A Device)<br>7.1.2 White LED (Class B Device)<br>7.1.3 Green and White LED(s) (Class C Device)<br>7.2 Location 2 LED(s)<br>7.2.1 Amber LED (SFF-TA-1006 and SFF-TA-1007)<br>7.2.2 Amber/Blue LED (SFF-TA-1008)                                                                                                                                                                        | 3433<br>3433<br>3534<br>3534<br>3534<br>3534<br>3534<br>3534                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8. | PCIe Electrical Requirements<br>8.1 Signal Integrity Requirements<br>8.1.1 Insertion Loss (IL)<br>8.1.2 Return Loss (RL)                                                                                                                                                                                                                                                                                                                      | <u>38</u> 37<br><u>38</u> 37<br><u>39</u> 38<br><u>39</u> 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>Enterprise and Datacenter Standard Form Factor Pin and</b> | Signal Specification                  | Page 6    |

|---------------------------------------------------------------|---------------------------------------|-----------|

|                                                               | Copyright © 20252024 SNIA. All rights | reserved. |

| <ul> <li>8.1.3 Power Sum Near End Crosstalk (PSNEXT)</li> <li>8.1.4 Power Sum Far End Crosstalk (PSFEXT)</li> <li>8.2 Transmitter and Receiver Sensitivity Eye Limits</li> <li>8.2.1 EDSFF Device Transmitter Eye Mask</li> <li>8.2.2 EDSFF Host Transmitter Eye Mask</li> <li>8.2.3 EDSFF Device Receiver Minimum Sensitivity</li> <li>8.2.4 EDSFF Host Receiver Minimum Sensitivity</li> <li>8.3 Test Fixtures</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>39</u> 38<br><u>39</u> 38<br><u>40</u> 39<br><u>40</u> 39<br><u>41</u> 40<br><u>41</u> 40<br><u>42</u> 41<br><u>42</u> 41                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>9. NIC Implementation (Informative)</li> <li>9.1 NIC Signals</li> <li>9.1.1 REFCLKp2, REFCLKn2, REFCLKp3, REFCLKn3</li> <li>9.1.2 PERST2#, PERST3#</li> <li>9.1.3 WAKE#</li> <li>9.1.4 PWRBRK0#</li> <li>9.1.5 BIF[02]#</li> <li>9.1.6 PRSNTA#</li> <li>9.1.7 PRSNTB[03]#</li> <li>9.1.8 AUX_PWR_EN</li> <li>9.1.9 MAIN_PWR_EN</li> <li>9.1.10 NIC_PWR_GOOD</li> <li>9.1.11 RBT Interface</li> <li>9.1.12 SLOT_ID[01]</li> <li>9.1.13 USB Interface (USB_DATp, USB_DATn)</li> <li>9.1.14 Scan Chain Interface</li> <li>9.2 3.3 Vaux consideration</li> </ul>                                                                                                                                                                                                                                                                       | 4342<br>4342<br>4342<br>4342<br>4342<br>4342<br>4342<br>4342                                                                                                       |

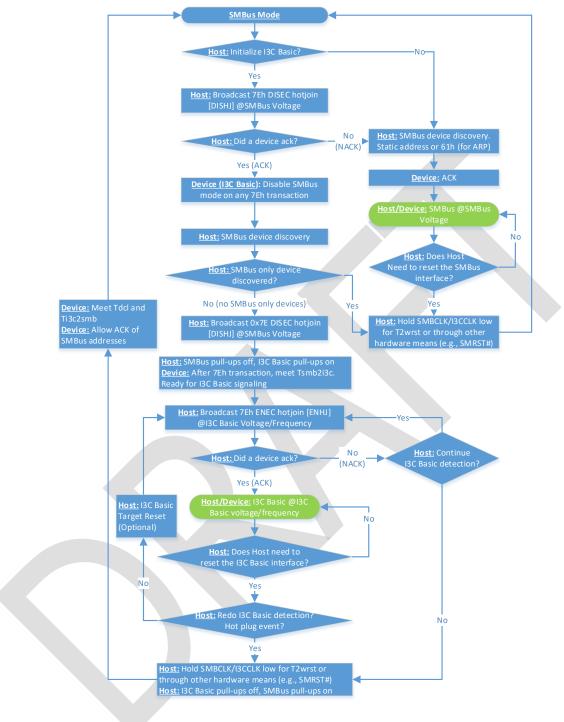

| 10. I3C Basic Implementation (Informative)<br>10.1 I3C Basic features and discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>46</u> 45<br><u>46</u> 45                                                                                                                                       |

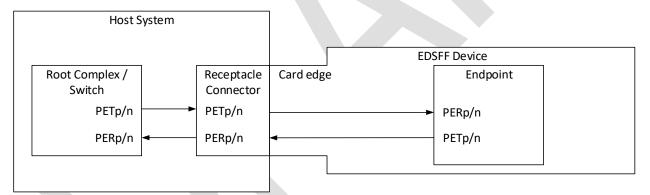

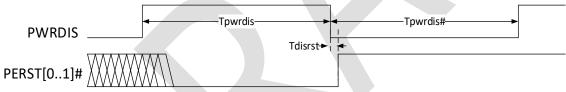

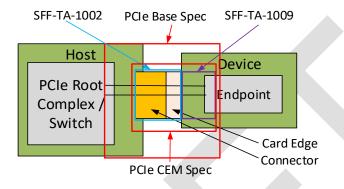

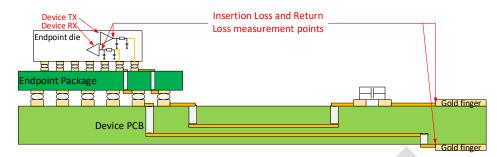

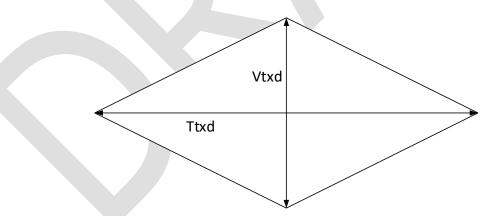

| <b>Figures</b><br>Figure 5-1. PET and PER Signal Connectivity Between Host and Device<br>Figure 6-1. EDSFF Device Timing Diagram for PWRDIS<br>Figure 6-2. EDSFF Device Timing Diagram for Transition to I3C Basic Signaling Voltage<br>Figure 7-1. Example Schematic for Controlling the Blue/Amber LED (Common Cathode)<br>Figure 7-2. Example Schematic for Controlling the Blue/Amber LED (Common Anode)<br>Figure 8-1. EDSFF Electrical Requirements Coverage<br>Figure 8-2. Example of Circuit Contributions to Insertion Loss and Return Loss<br>Figure 8-3. Example of PSNEXT Test Configuration for Device<br>Figure 8-4. Example of PSFEXT Victim and Aggressors<br>Figure 8-5. Eye Diagram for EDSFF Device Transmitter<br>Figure 8-6. Eye Diagram for EDSFF Host Transmitter<br>Figure 10-1. SMBus to I3C Basic transition flow | 17 <del>16</del><br>3130<br>3332<br>3635<br>3736<br>3837<br>3938<br>3938<br>3938<br>4039<br>4039<br>4140<br>4746                                                   |

| TablesTable 5-1. EDSFF Connector Pin ListTable 5-2. PCIe lanes connectivity in single and dual port implementations (without lane reversal)Table 5-3. EDSFF x4 (1C) Connector PinoutTable 5-4. EDSFF x8 (2C) Connector PinoutTable 5-5. EDSFF x16 (4C) Connector PinoutTable 5-6. EDSFF x16 With Additional Sideband (4C+) Connector PinoutTable 6-1. 12 V Power Supply RequirementsTable 6-2. 3.3 Vaux Power Supply RequirementsTable 6-3. EDSFF Device Timing requirementsTable 6-4. DC Specification for 3.3 V Logic Signaling                                                                                                                                                                                                                                                                                                           | <u>1413</u><br><u>18</u> 17<br><u>2120</u><br><u>2322</u><br><u>2524</u><br><u>2524</u><br><u>2726</u><br><u>3029</u><br><u>3029</u><br><u>3130</u><br><u>3231</u> |

Enterprise and Datacenter Standard Form Factor Pin and Signal Specification Page 7

Copyright © 20252024 SNIA. All rights reserved.

| Table 6-5. DC Specification for I3C Basic Logic Signaling                             | <u>32</u> 31 |

|---------------------------------------------------------------------------------------|--------------|

| Table 6-6. I3C Basic Timing Requirements                                              | <u>32</u> 31 |

| Table 7-1. LED Requirements                                                           | <u>34</u> 33 |

| Table 7-2. Device-driven LED Implementation                                           | <u>34</u> 33 |

| Table 7-3. LED and Device State Per Function for Green LED (Class A Device)           | <u>35</u> 34 |

| Table 7-4. LED and Device State Per Function for White LED (Class B Device)           | <u>35</u> 34 |

| Table 7-5. LED and Device State Per Function for Green and White LED (Class C Device) | <u>35</u> 34 |

| Table 7-6. LED and Device State per Function for Amber LED                            | <u>36</u> 35 |

| Table 7-7. LED and Device State per Function for Amber/Blue LED                       | <u>36</u> 35 |

| Table 8-1. Summary of Signal Integrity Requirements                                   | <u>38</u> 37 |

| Table 8-2. EDSFF Device Transmitter Eye Mask for PCIe at 16.0 GT/s                    | <u>40</u> 39 |

| Table 8-3. EDSFF Device Transmitter Eye Mask for PCIe at 32.0 GT/s                    | <u>41</u> 40 |

| Table 8-4. EDSFF Device Transmitter Eye Mask for PCIe at 64.0 GT/s                    | <u>41</u> 40 |

| Table 8-5. EDSFF Host Transmitter Eye Mask for PCIe at 16.0 GT/s                      | <u>41</u> 40 |

| Table 8-6. EDSFF Host Transmitter Eye Mask for PCIe at 32.0 GT/s                      | <u>41</u> 40 |

| Table 8-7. EDSFF Host Transmitter Eye Mask for PCIe at 64.0 GT/s                      | <u>41</u> 40 |

# 1. Scope

The following specification defines the requirements for a device that is optimized for Enterprise and Datacenter applications.

# 1.1 Application Specific Criteria

This specification defines the pin list and pin placement, function of the pins, device specific electrical requirements, and specific features of enterprise and datacenter-based devices. This specification relies on SFF-TA-1002 for the connector mechanicals and SFF-TA-1006, SFF-TA-1007, and SFF-TA-1008 form factor specifications for the form factor mechanicals.

# 2. References and Conventions

# 2.1 Industry Documents

The following documents are relevant to this specification:

- PCI Express<sup>®</sup> (PCIe<sup>®</sup>) Base Specification, revision 6.2 available from <u>https://www.pcisig.com</u>.

- PCI Express<sup>®</sup> (PCIe<sup>®</sup>) Card Electromechanical Specification, revision 5.1, Version 1.0 available from <a href="https://www.pcisig.com">https://www.pcisig.com</a>.

- System Management Bus (SMBus) Specification, Version 3.2, available from http://smbus.org.

- SNIA SFF-TA-1002 Card Edge multilane protocol agnostic connector specification available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- SNIA SFF-TA-1006 Enterprise and Datacenter 1U Short device Form Factor available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- SNIA SFF-TA-1007 Enterprise and Datacenter 1U Long device Form Factor available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- SNIA SFF-TA-1008 Enterprise and Datacenter Form Factor for a 3" Media Device available at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>.

- Compute Express Link<sup>™</sup> (CXL<sup>™</sup>) Specification available from <u>https://www.computeexpresslink.org/</u>

- CIE 127-2007 Measurement of LEDs available at https://www.techstreet.com/cie/searches/29093398

- NVM Express<sup>®</sup> Base Specification available at https://nvmexpress.org/.

- MIPI™ Alliance Specification for I3C Basic, Version 1.0 available at <u>https://www.mipi.org</u>.

- MIPI<sup>™</sup> Alliance Specification I3C Basic Slave Reset Addendum available at <u>https://resources.mipi.org/mipi-i3c-basic-slave-reset-download</u>.

- Open Compute Project OCP NIC 3.0 Design Specification, revision 1.2.0 available at <a href="https://www.opencompute.org/wiki/Server/Mezz">https://www.opencompute.org/wiki/Server/Mezz</a>.

- Distributed Management Task Force (DMTF) DSP0222 Network Controller Sideband Interface (NC-SI) Specification, Rev 1.1.0 available at https://www.dmtf.org/sites/default/files/standards/documents/DSP0222 1.1.0.pdf

- United Serial Bus (USB) Specification, Version 2.0, available from https://usb.org.

# 2.2 Sources

The complete list of SFF documents which have been published, are currently being worked on, or that have been expired by the SFF Committee can be found at <u>https://www.snia.org/sff/specifications</u>. Suggestions for improvement of this specification are welcome and should be submitted to <u>https://www.snia.org/feedback</u>.

## 2.3 Conventions

The following conventions are used throughout this document:

**DEFINITIONS:** Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

**ORDER OF PRECEDENCE:** If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

**LISTS:** Lists sequenced by lowercase or uppercase letters show no ordering relationship between the listed items.

EXAMPLE 1 - The following list shows no relationship between the named items:

a. red (i.e., one of the following colors):

A. crimson; or

<u>B. pink;</u>

b. blue; or

<u>c. green.</u>

Lists sequenced by numbers show an ordering relationship between the listed items.

EXAMPLE 2 -The following list shows an ordered relationship between the named items:

<u>1. top;</u>

middle; and

3. bottom.

Lists are associated with an introductory paragraph or phrase and are numbered relative to that paragraph or phrase (i.e., all lists begin with an a. or 1. entry).

**DIMENSIONING CONVENTIONS:** The dimensioning conventions are described in ASME-Y14.5, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

**NUMBERING CONVENTIONS:** The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

# 3. Keywords, Acronyms, and Definitions

For the purposes of this document, the following keywords, acronyms, and definitions apply.

# 3.1 Keywords

May: Indicates flexibility of choice with no implied preference.

May or may not: Indicates flexibility of choice with no implied preference.

**Obsolete:** Indicates that an item was defined in prior specifications but has been removed from this specification.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be done in the same way as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Prohibited:** Describes a feature, function, or coded value that is defined in a referenced specification to which this SFF specification makes a reference, where the use of said feature, function, or coded value is not allowed for implementations of this specification.

**Reserved:** Defines the signal on a connector contact when its actual function is set aside for future standardization. It is not available for vendor specific use. Where this term is used for bits, bytes, fields, and code values; the bits, bytes, fields, and code values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Restricted:** Refers to features, bits, bytes, words, and fields that are set aside for other standardization purposes (e.g., entities). If the context of the specification applies the restricted designation, then the restricted bit, byte, word, or field shall be treated as a reserved bit, byte, word, or field (e.g., a restricted byte uses the same value as defined for a reserved byte).

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

## 3.2 Acronyms and Abbreviations

**EDSFF:** Enterprise and Datacenter Standard Form Factor **NVM:** Non-Volatile Memory **SSD:** Solid State Drive

## 3.3 Definitions

**Card:** Refers to the device plugged into a connector

**Chiclet:** A building block for use in naming convention defined as 8 differential pairs of data signals.

**Contact Sequence:** The order that a device card edge pin makes physical contact to the host connector.

**Device:** Refers to the interface target.

**Dual Port:** When enabled, the device is configured with a PCIe port A and a PCIe port B. This is known as Dual Port mode. When disabled, all lanes form a single PCIe port A. In dual port mode, the two ports must operate independently. Any interaction between the two ports is outside the scope of the specification.

**Endpoint:** The PCIe interface target logic located on the Device.

**Host:** Refers to the interface source or initiator.

**nC:** Connector naming (1C, 2C, 4C) convention that indicates the number of Chiclets. This convention is used because common naming such as "x4, x8" etc. implies symmetrical data transfer in each direction.

**Root Complex:** The initiator source logic located on the Host.

**SRIS:** Acronym for Separate Reference clock Independent Spread spectrum clocking. This is a PCI Express feature that allows independent reference clocks for host and device. In this implementation, the host does not need to provide the reference clock and each independent source supports Spread Spectrum Clocking (SSC).

**SRNS:** Acronym for Separate Reference clock with No Spread spectrum clocking. This is a PCI Express feature that allows independent reference clocks for host and device. In this implementation, the host does not need to provide the reference clock and Spread Spectrum Clocking (SSC) is not enabled by either source.

**Switch:** A logic component located on the Host used to connect between a Root Complex and 1 or more Endpoints.

# 4. General Description

The Enterprise and Datacenter Standard Form Factor Specification is meant for serviceable devices that connect electrically to the system through a card edge connector as defined in SFF-TA-1002. This specification defines the following features:

- Support for multiple form factors:

- SFF-TA-1006 Enterprise and Datacenter 1U Short Device Form Factor

- SFF-TA-1007 Enterprise and Datacenter 1U Long Device Form Factor

- SFF-TA-1008 Enterprise and Datacenter Form Factor for a 3" Media Device

- PCIe support for existing and future specifications

- Supports PCIe 6.2 specification (up to 64.0 GT/s signaling).

- Single port operation: One (1) x1, x2, x4, x8, or x16 PCIe port supported

- Dual port: Two (2) x2, two (2) x4, or two (2) x8 PCIe ports supported

- 4 connector types using SFF-TA-1002

- A 56-pin receptacle supporting Four (4) Tx and Rx PCIe lanes (1C).

- An 84-pin receptacle supporting Eight (8) Tx and Rx PCIe lanes (2C).

- A 140-pin receptacle supporting Sixteen (16) Tx and Rx PCIe lanes (4C).

- A 168-pin receptacle supporting Sixteen (16) Tx and Rx PCIe lanes with additional sideband (4C+).

- Hot-plug (add and remove) capable connector and pin out

- Common clock with options for SRIS and SRNS support by both host and device

- Support for sideband management over SMBus or I3C Basic.

- Connector supports up to 80W sustained operation (actual power is specified per form factor).

# 5. Signal List

This chapter covers the signal summary, definitions, and signal placement for the EDSFF connectors. Signal directions (I/O) are with respect to the host and the signals are mandatory for the device unless otherwise specified.

| Interface  | Signal Name        | Host I/O | Function                                                                                                                                                                       |  |  |

|------------|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Deutor and | ower and 12 V      |          | +12 V power                                                                                                                                                                    |  |  |

| Power and  | 3.3 Vaux           | 0        | +3.3 V power                                                                                                                                                                   |  |  |

| Grounds    | GND                | 0        | Return current path                                                                                                                                                            |  |  |

|            | PETp0, PETn0       |          |                                                                                                                                                                                |  |  |

|            | PETp1, PETn1       |          |                                                                                                                                                                                |  |  |

|            | PETp2, PETn2       |          |                                                                                                                                                                                |  |  |

|            | PETp3, PETn3       |          |                                                                                                                                                                                |  |  |

|            | PETp4, PETn4       |          |                                                                                                                                                                                |  |  |

|            | PETp5, PETn5       |          | PCIe TX Differential signals defined by the PCI Express                                                                                                                        |  |  |

|            | PETp6, PETn6       |          | Card Electromechanical Specification. PETp/n[03] are                                                                                                                           |  |  |

|            | PETp7, PETn7       | 0        | supported in the x4, x8, and x16 connectors.                                                                                                                                   |  |  |

|            | PETp8, PETn8       | Ū        | PETp/n[47] are supported with the x8 and x16                                                                                                                                   |  |  |

|            | PETp9, PETn9       |          | connectors. PETp/n[815] are supported only with the                                                                                                                            |  |  |

|            | PETp10, PETn10     |          | x16 connector.                                                                                                                                                                 |  |  |

|            | PETp11, PETn11     |          |                                                                                                                                                                                |  |  |

|            | PETp12, PETn12     |          |                                                                                                                                                                                |  |  |

|            | PETp13, PETn13     |          |                                                                                                                                                                                |  |  |

|            | PETp14, PETn14     |          |                                                                                                                                                                                |  |  |

|            | PETp15, PETn15     |          |                                                                                                                                                                                |  |  |

|            | PERp0, PERn0       |          |                                                                                                                                                                                |  |  |

|            | PERp1, PERn1       |          |                                                                                                                                                                                |  |  |

|            | PERp2, PERn2       |          |                                                                                                                                                                                |  |  |

| PCIe       | PERp3, PERn3       |          |                                                                                                                                                                                |  |  |

|            | PERp4, PERn4       |          |                                                                                                                                                                                |  |  |

|            | PERp5, PERn5       |          | PCIe RX Differential signals defined by the PCI Express                                                                                                                        |  |  |

|            | PERp6, PERn6       | Ι        | Card Electromechanical Specification. PERp/n[03] are                                                                                                                           |  |  |

|            | PERp7, PERn7       |          | supported in the x4, x8, and x16 connectors.                                                                                                                                   |  |  |

|            | PERp8, PERn8       |          | PERp/n[47] are supported with the x8 and x16 supporters $PEPn/n[8, 15]$ are supported and with the                                                                             |  |  |

|            | PERp9, PERn9       |          | connectors. PERp/n[815] are supported only with the x16 connector.                                                                                                             |  |  |

|            | PERp10, PERn10     |          | XIO CONNECTOI.                                                                                                                                                                 |  |  |

|            | PERp11, PERn11     |          |                                                                                                                                                                                |  |  |

|            | PERp12, PERn12     |          |                                                                                                                                                                                |  |  |

|            | PERp13, PERn13     |          |                                                                                                                                                                                |  |  |

|            | PERp14, PERn14     |          |                                                                                                                                                                                |  |  |

|            | PERp15, PERn15     |          | DCTa Deference Cleak signals defined by the DCT 5                                                                                                                              |  |  |

|            | REFCLKp0, REFCLKn0 | 0        | PCIe Reference Clock signals defined by the <i>PCI Express Base Specification</i> .                                                                                            |  |  |

|            | PERST0#            | 0        | PE-Reset is a fundamental reset to the device defined as PERST# by the <i>PCI Express Base Specification</i> .                                                                 |  |  |

|            | REFCLKp1, REFCLKn1 | 0        | PCIe Reference Clock signals defined by the <i>PCI Express</i><br><i>Base Specification</i> . This clock is for dual port mode only<br>and is only used if DUALPORTEN# is low. |  |  |

#### Table 5-1. EDSFF Connector Pin List

| Interface   | Signal Name                              | Host I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | PERST1#/CLKREQ#                          | I/O      | PERST1#: PE-Reset is a fundamental reset to the device<br>defined as PERST# by the <i>PCI Express Base Specification</i> .<br>If dual port mode is supported by the device, PERST1# is<br>only used when DUALPORTEN# is low.<br>CLKREQ#: Clock Request is a reference clock request<br>signal defined by the <i>PCI Express Base Specification</i> . It<br>may be supported by a device in single port mode only.<br>If CLKREQ# is supported by the host and the device, then<br>the signal is Open Drain with a pull up on host. |

|             | PRSNT0#                                  | Ι        | Active low signal. This signal indicates to the host that the device is electrically attached.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | PRSNT1#                                  | I        | Active low signal. This signal is available in the x8 and x16 versions of the connector as a $2^{nd}$ presence signal to indicate to the host that the device is electrically attached. This signal is not available in the x4 version of the connector.                                                                                                                                                                                                                                                                          |

|             | PRSNT2#                                  | Ι        | Active low signal. This signal is available in the x16 connector as a 3 <sup>rd</sup> presence signal to indicate to the host that the device is electrically attached. This signal is not available in the x4 and x8 versions of the connector.                                                                                                                                                                                                                                                                                  |

| Sideband    | SMBCLK/I3CCLK                            | 0        | SMBCLK: Open Drain with pull-up on host. SMBus Clock.<br>I3CCLK: Active high push-pull and open drain signal. I3C<br>Basic Clock.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Signals     | SMBDATA/I3CDATA                          | I/O      | SMBDATA: Open Drain with pull-up on host. SMBus Data.<br>I3CDATA: Active high push-pull and open drain signal.<br>I3C Basic Data.                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | SMRST#                                   | 0        | Active low signal. SMRST# is a reset for the management interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | DUALPORTEN#                              | 0        | Open drain. Pull-up on device. This signal indicates if dual port mode is supported by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | LED                                      | 0        | Active high signal. This signal is used to drive the amber<br>or amber/blue LED state from the host to the device.                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | PWRDIS                                   | 0        | Active high signal. Power Disable notifies the device to turn off all systems connected to 12 V power.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | MFG                                      |          | Manufacturing mode, signal used only for the manufacturing of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | RFU                                      |          | Reserved for Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |