DRAFT SFF-8679 Rev 1.8.54

6

7

8

9

10 11

12

13

14 15 16

17

18 19

20 21 22

23

24 25

26

31 32

33

34 35

36 37 38

40

39

Specification for

SFF-8679

# **QSFP+ 4X Hardware and Electrical Specification**

-MarchJanuary 180, 2025 Rev 1.8.<u>5</u>4

SECRETARIAT: SFF-TA-TWG This draft specification is made available for public review at <a href="https://www.snia.org/sff/specifications">https://www.snia.org/sff/specifications</a>. Comments may be submitted at https://www.snia.org/feedback, Comments received will be considered for inclusion in future revisions of this specification.

This document has been released by SNIA. The SFF TWG believes that the ideas, methodologies, and technologies described in this document are technically accurate and are appropriate for widespread distribution.

The description of the connector in this specification does not assure that the specific component is available from connector suppliers. If such a connector is supplied, it should comply with this specification to achieve interoperability between suppliers.

ABSTRACT: This specification defines the contact pads, the electrical, power supply, ESD and thermal characteristics of the pluggable QSFP+ module or cable plug.

There are multiple generations of QSFP+ that reference this specification:

```

SFF-8635 QSFP+ 4X 10 Gb/s Pluggable Transceiver Solution (QSFP10)

SFF-8685 QSFP+ 4X 14 Gb/s Pluggable Transceiver Solution (QSFP14)

SFF-8665 QSFP+ Pluggable Transceiver Solution (QSFP+)

SFF-TA-1027 QSFP2 Cage, Connector and Module Specification

```

This specification supersedes the base electrical content of SFF-8436 QSFP+ 10Gb/s 4X Pluggable Transceiver.

This document provides a common specification for systems manufacturers, system integrators, and suppliers.

POINTS OF CONTACT: SNIA Technical Council Managing Director

Email: TCMD@snia.org

**EDITORS:** Vera Koleva, Coherent

Chairman SFF-TA-TWG

Email: SFF-Chair@snia.org

#### **Intellectual Property**

The user's attention is called to the possibility that implementation of this specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith.

This specification is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published.

The SNIA IP Review Process is still in progress. If IP disclosures that affect this specification are made during this process, this specification may be withdrawn.

Additional information can be found at the following locations:

Results of IP Disclosures: <a href="https://www.snia.org/sffdisclosures">https://www.snia.org/sffdisclosures</a>

SNIA IP Policy: <a href="https://www.snia.org/ippolicy">https://www.snia.org/ippolicy</a>

#### Copyright

SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and

display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing <a href="mailto:copyright\_request@snia.org">copyright\_request@snia.org</a>. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

#### **Disclaimer**

The information contained in this publication is subject to change without notice. SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to https://www.snia.org/feedback/.

## Foreword

1

2

3

4

5 6

7

15 16

17

18

19

20

21

22 23

24

25

26

27

28

29

30 31

32 33

34 35

36

37

38

39

40

41 42

43

44 45

46

47

48 49

50 51

52

53

54 55 The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, as well as since SFF's transition to SNIA in 2016, the membership has included a mix of companies which are leaders across the industry.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at <a href="https://www.snia.org/join">https://www.snia.org/join</a>.

#### **Revision History**

Rev 1.5:

- Moved referenced SFF specs to 2.1 Industry Documents and expanded the list.

#### Rev 1.6:

- Updated Figure 1 to show retimers.

- Removed two-wire interface timing diagram which is now in SFF-8636.

- Complete rewrite of power supply section to add support for Power Classes 5 to 7.

- Added section 8 "Timing Requirements".

Rev 1.7

- Editorial only, no technical changes.

Rev 1.8

- Converted to SNIA SFF template.

- Editorial updates throughout.

- Title changed to "Hardware and Electrical" to better reflect contents

- Updated abstract

- Updated editor contact information.

- Section 1 Scope rewrote to better reflect content.

- <u>Section 2 References</u> replaced several entries with updated document numbers and names.

- Section 2.3 Acronyms deleted several unused entries and added several new ones based on content.

- Section 3 General Description Rewrote most of this section to reflect updated content. Added several relevant applications to Table 3-1.

- <u>Section 4 Compliance Testing</u> updated Figure 4-1 and corrected test point descriptions in Table 4-1.

- Section 5 Electrical Specification

- Updated Figure 5-1 and Table 5-1 to show the new dual-purpose signals LPMode/TxDis and IntL/RxLOSL on pads 31 and 28 respectively. Rewrote Note 2 of Table 5-1 for clarity.

- Replaced "pin" by "pad" throughout

- Replaced Figures 5-2 and 5-3 to better reflect current applications.

- Extensive updates of Section 5.3 describing Low Speed Signals.

- Updates to Table 5-2 to explain SCL and SDA electrical requirements and maximum pullup resistor values for 400 kHz operation.

- Significant revisions to text in 5.4 Low Speed Signal Electrical Specifications and 5.5 High Speed Signal Electrical Specifications.

- Re-ordered and rewrote section 5.6 Power Supply Requirements including adding a new Power Class 8 with a maximum power limited only by the connector current rating.

- <u>Section 6 Mechanical and Board Definition</u> cleaned up this section to reference the relevant documents instead of including non hardware/electrical features.

- Section 7 Environmental and Temperature added a "custom" temperature class for modules that do not comply with any of the legacy case temperature ranges, e.g., hyperscale data center applications.

- Section 8 Timing Requirements

- Major updates to Table 8-1 including re-writes of many entries in the "Conditions"

DRAFT SFF-8679 Rev 1.8.<u>5</u>4

#### Contents

| 2        | 1.          | Scope                                                                                     | 10           |

|----------|-------------|-------------------------------------------------------------------------------------------|--------------|

| 3        | 2           | References, Conventions, Keywords, Definitions                                            | 10           |

| 4        |             | 2.1 Industry Documents                                                                    | 10           |

| 5        |             | 2.2 Technical References                                                                  | <u>-</u> -11 |

| 6        |             | 2.3 Sources                                                                               | <br>11       |

| 7        |             | 2.4 Conventions                                                                           | 12           |

| 8        | 3           | Keywords, Acronyms, and Definitions                                                       | 13           |

| 9        | <u> </u>    | 3.1 Keywords                                                                              | 13           |

| 10       |             | 3.2 Acronyms and Abbreviations                                                            | 13           |

| 11       |             | 3.3 Definitions                                                                           | 15           |

| 12       | 4.          | General Description                                                                       | 16           |

| 13       |             | 4.1 Configuration Overview/Descriptions                                                   | 16           |

|          | _           |                                                                                           |              |

| 14       | <u>5.</u>   | Compliance boards and reference points                                                    | 17           |

| 15       | 6.          | Electrical Specification                                                                  | 18           |

| 16       |             | 6.1 Electrical Connector                                                                  | 18           |

| 17       |             | 6.2 QSFP Example Circuits                                                                 | 21           |

| 18       |             | 6.3 Low Speed Signal Descriptions                                                         | 23           |

| 19       |             | 6.3.1 ModSelL                                                                             | 23           |

| 20       |             | 6.3.2 ResetL                                                                              | 23           |

| 21       |             | 6.3.3 LPMode/TxDis                                                                        | 23           |

| 22       |             | 6.3.4 ModPrsL                                                                             | 24           |

| 23       |             | 6.3.5 IntL/RxLOSL                                                                         | 24           |

| 24       |             | 6.4 Low Speed Signal Electrical Specifications                                            | 24           |

| 25       |             | 6.4.1 Low Speed Signaling                                                                 | 24           |

| 26       |             | 6.4.2 Low Speed Signal Timing                                                             | 26           |

| 27       |             | 6.5 High Speed Signal Electrical Specifications                                           | 27           |

| 28       |             | 6.5.1 Rxip and Rxin                                                                       | 27           |

| 29       |             | 6.5.2 Tx/p and Tx/n                                                                       | 27           |

| 30       |             | 6.6 Power Supply Requirements                                                             | 29<br>29     |

| 31<br>32 |             | 6.6.1 Host Board Power Supply Filtering 6.6.2 Power Classes and Maximum Power Consumption | 29<br>30     |

| 33       |             | 6.6.3 Module Power Supply Specification                                                   | 30<br>32     |

| 34       |             | 6.6.4 Host Board Power Supply Noise Output                                                | 32<br>38     |

| 35       |             | 6.6.5 Module Power Supply Noise Output                                                    | 39           |

| 36       |             | 6.6.5.1 QSFP+ Module Power Supply Noise Output Test Method based on SFF-8431              | 39<br>39     |

| 37       |             | 6.6.5.2 QSFP112/QSFP224 Module Power Supply Noise Output Test Method                      | 33<br>40     |

| 38       |             | 6.6.6 Module Power Supply Noise Tolerance                                                 | 10<br>40     |

| 39       |             | 6.6.6.1 QSFP+ Module Power Supply Noise Tolerance Test Method based on SFF-8431           | 40           |

| 40       |             | 6.6.6.2 QSFP112/QSFP224 Module Power Supply Noise Tolerance Test Method                   | 41           |

| 41       |             | 6.6.6.3 Module Power Supply Noise Tolerance Test Method using Commercial Injector Probe   | 42           |

| 42       |             | 6.7 ESD                                                                                   | 43           |

| 43       | 7.          | Mechanical and Board Definition                                                           | 44           |

| 44       |             | 7.1 Mechanical general                                                                    | 44           |

| 45       |             | 7.2 Color Coding and Labeling of Modules                                                  | <br>45       |

| 46       |             | 7.3 Optical Interface                                                                     | 3<br>47      |

| 47       |             | 7.3.1 MPO Optical Cable Connection                                                        | 48           |

| 48       |             | 7.3.2 Dual LC Optical Cable Connection                                                    | 48           |

| 49       | <u>8.</u> E | Environmental and Temperature                                                             | 49           |

|          |             |                                                                                           |              |

| 1        | 8.1 Temperature Requirements                                                         | 49             |

|----------|--------------------------------------------------------------------------------------|----------------|

| 2        | 9. Timing Requirements                                                               | 49             |

| 3        | 9.1 Control and Status Timing Requirements                                           | 50             |

| 4        | 9.2 Squelch and Tx/Rx Disable Assert, Deassert and Enable/Disable Timing             | 50<br>53       |

| •        | 5.2 Squelett drift 17/10/ bisdible 163erty bedssere drift Endble/ bisdible 11/11/11g | 55             |

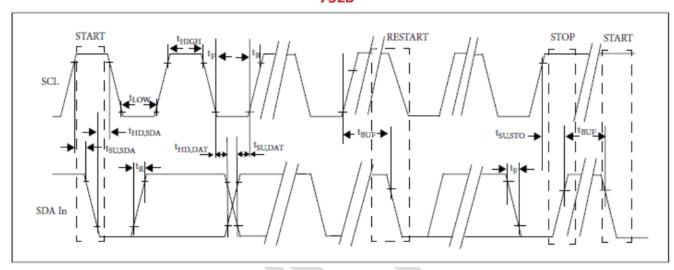

| 5        | Appendix A. Two-wire Interface Timing                                                | 54             |

| 6        | A.1 Timing Diagram                                                                   | 54             |

| 7        | A.2 Timing Parameters                                                                | 55             |

| •        |                                                                                      | _              |

| 8        | 1.—Scope                                                                             | <i>_</i>       |

| 9        | 2.—References, Conventions, Keywords, Definitions                                    |                |

| 10       |                                                                                      | <del></del>    |

| 11       | 2.1—Industry Documents 2.2—Technical References                                      | 8              |

| 12       | 2.3—Sources                                                                          | 8              |

| 13       | 2.1 Conventions                                                                      | 9              |

|          |                                                                                      |                |

| 14       | 3. Keywords, Acronyms, and Definitions                                               | 10             |

| 15       | 3.1—Keywords                                                                         | 10             |

| 16       | 3.2—Acronyms and Abbreviations                                                       | 10             |

| 17       | 3.3—Definitions                                                                      | 12             |

| 10       | 4 6 15 11                                                                            | 40             |

| 18       | 4. General Description                                                               | 13             |

| 19       | 4.1—Configuration Overview/Descriptions                                              | 13             |

| 20       | 5. Compliance boards and reference points                                            | 14             |

|          |                                                                                      |                |

| 21       | 6.—Electrical Specification                                                          | <del>15</del>  |

| 22       | 6.1—Electrical Connector                                                             | <del>15</del>  |

| 23       | 6.2—QSFP Example Circuits                                                            | 18             |

| 24       | 6.3—Low Speed Signal Descriptions                                                    | <del>20</del>  |

| 25       | 6.3.1—ModScIL                                                                        | <del>20</del>  |

| 26       | 6.3.2—ResetL                                                                         | <del>20</del>  |

| 27       | 6.3.3—LPMode/TxDis                                                                   | <del>20</del>  |

| 28       | 6.3.1 ModPrsL                                                                        | <del>21</del>  |

| 29       | 6.3.5—IntL/RxLOSL                                                                    | <del>21</del>  |

| 30       | 6.4—Low Speed Signal Electrical Specifications                                       | <del>21</del>  |

| 31       | 6.4.1—Low Speed Signaling                                                            | <del>21</del>  |

| 32       | 6.4.2—Low Speed Signal Timing                                                        | <del>23</del>  |

| 33       | 6.5 High Speed Signal Electrical Specifications                                      | 24             |

| 34       | 6.5.1—Rxip and Rxin                                                                  | 24             |

| 35       | 6.5.2—Txip and Txin                                                                  | <del>24</del>  |

| 36       | 6.6—Power Supply Requirements                                                        | <del>25</del>  |

| 37       | 6.6.1—Host Board Power Supply Filtering                                              | <del>25</del>  |

| 38       | 6.6.2—Power Classes and Maximum Power Consumption                                    | <del>26</del>  |

| 39       | 6.6.3 Module Power Supply Specification                                              | <del>28</del>  |

| 40       | 6.6.1 Host Board Power Supply Noise Output                                           | 31             |

| 41       | 6.6.5 Module Power Supply Noise Output                                               | <del>32</del>  |

| 42       | 6.6.5.1—QSFP+ Module Power Supply Noise Output Test Method based on SFF-8431         | <del>32</del>  |

| 43       | 6.6.5.2—QSFP112/QSFP224 Module Power Supply Noise Output Test Method                 | <del>32</del>  |

| 44<br>45 | 6.6.6 Module Power Supply Noise Tolerance                                            | 33             |

| 45<br>46 | 6.6.6.1 — QSFP+ Module Power Supply Noise Tolerance Test Method based on SFF-843     | 33             |

| 46<br>47 | 6.6.6.2 — QSFP112/QSFP224 Module Power Supply Noise Tolerance Test Method            | 33<br>33<br>35 |

| 47<br>40 | 6.6.6.3 — Module Power Supply Noise Tolerance Test Method using Commercial Injecto   |                |

| 48       | <del>6.7—ESD</del>                                                                   | <del>36</del>  |

| 40       | 7 Machanical and Roard Definition                                                    | 27             |

| ۱ ،      | 7.1 Machanical ganaval                                                                      | 27                                     |

|----------|---------------------------------------------------------------------------------------------|----------------------------------------|

| 1        | 7.1—Mechanical general                                                                      | <del>37</del>                          |

| 2        | 7.2—Color Coding and Labeling of Modules                                                    | <del>38</del>                          |

| 3        | 7.3 Optical Interface                                                                       | <del>39</del>                          |

| 4        | 7.3.1—MPO Optical Cable Connection                                                          | <del>40</del>                          |

| 5        | 7.3.2—Dual LC Optical Cable Connection                                                      | 40                                     |

| 6        | 8.—Environmental and Temperature                                                            | 41                                     |

| 7        | 8.1—Temperature Requirements                                                                | <del>41</del>                          |

| <b>'</b> | 6.1—Temperature requirements                                                                | 71                                     |

| 8        | 9. Timing Requirements                                                                      | <del>41</del>                          |

| 9        | 9.1—Control and Status Timing Requirements                                                  | <del>42</del>                          |

| 10       | 9.2—Squelch and Tx/Rx Disable Assert, Deassert and Enable/Disable Timing                    | 45                                     |

|          |                                                                                             |                                        |

| 11       | Appendix A. Two-wire Interface Timing                                                       | <del>46</del>                          |

| 12       | A.1 Timing Diagram                                                                          | 46                                     |

| 13       | A.2 Timing Parameters                                                                       | <del>47</del>                          |

| 14       |                                                                                             |                                        |

| 15       |                                                                                             |                                        |

| 16       | Figures                                                                                     |                                        |

| 17       | Figure 3-1 Plug and Receptacle Definition                                                   | 15                                     |

| 18       | Figure 4-1 Application reference model                                                      | 16                                     |

| 19       | Figure 5-1 Reference Points and Compliance Boards                                           | 17                                     |

| 20       | Figure 6-1 Module Pad Layout                                                                | 19                                     |

| 21       | Figure 6-2 Example: Host Board Schematic for Optical Modules                                | 21                                     |

| 22       | Figure 6-3 Example: Host Board Schematic for Passive Copper Cables                          | 22                                     |

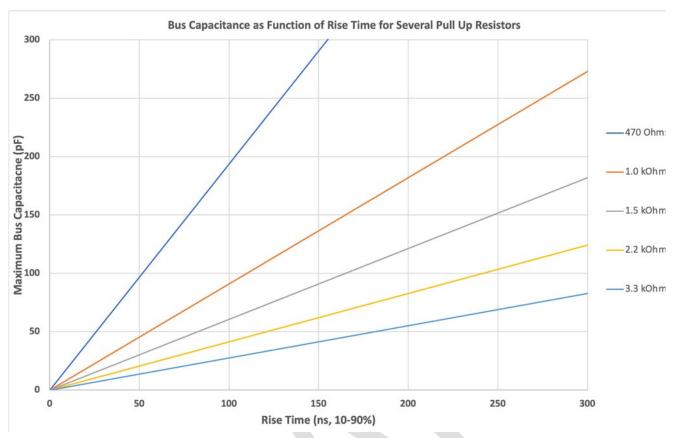

| 23       | Figure 6-4 SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times        | 26                                     |

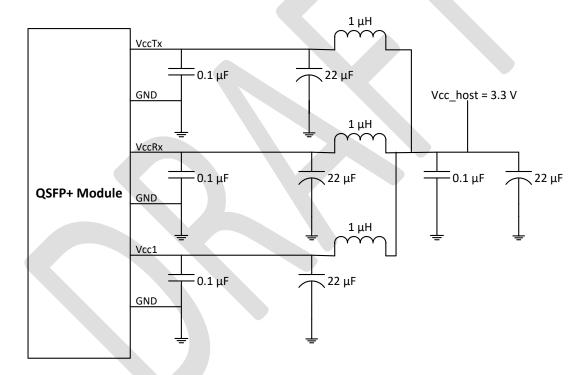

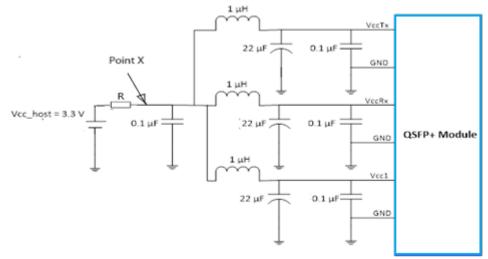

| 24       | Figure 6-5 Recommended Host Board Power Supply Filtering                                    | 29                                     |

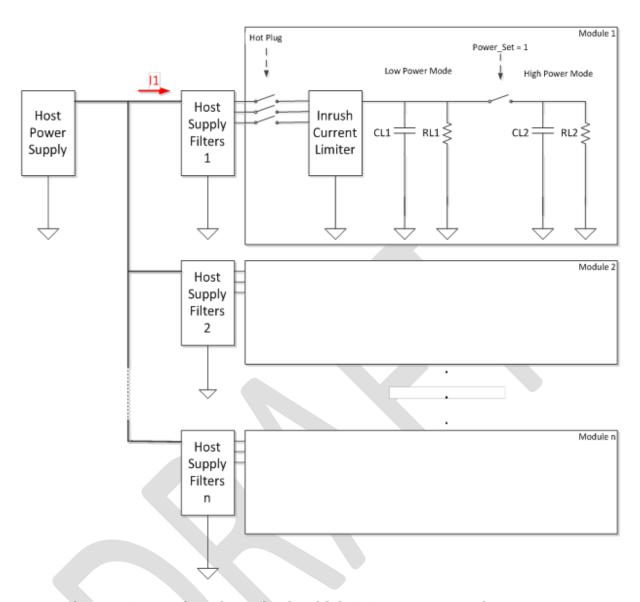

| 25       | Figure 6-6 Example: Schematic of multiple QSFP+ power supply arrangement                    | 30                                     |

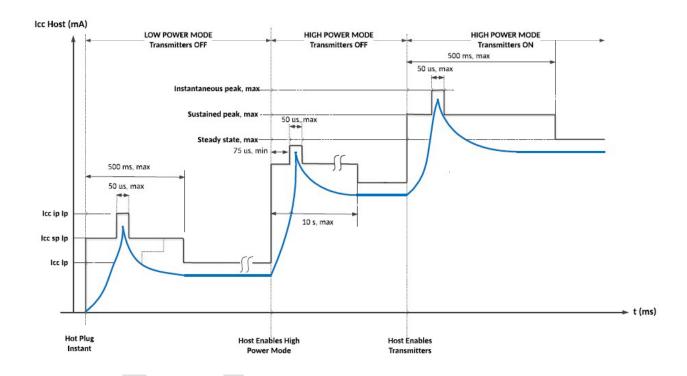

| 26       | Figure 6-7 QSFP+ Inrush Current Timing                                                      | 33                                     |

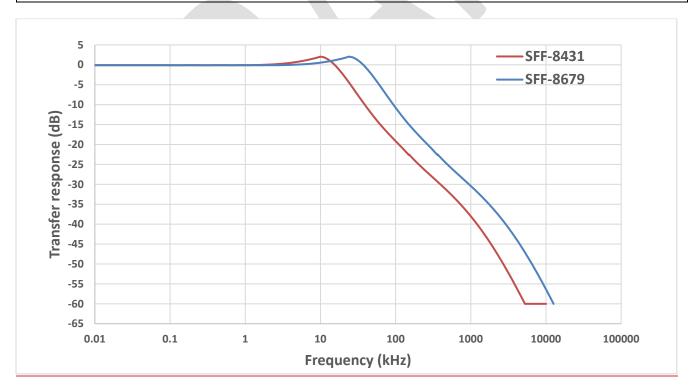

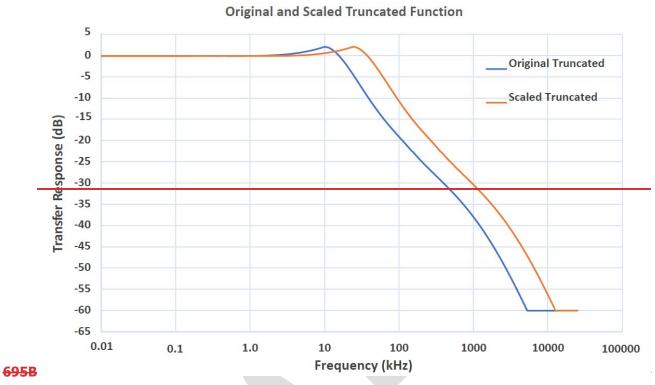

| 27       | Figure 6-8 Truncated Transfer Response for Host Board Power Supply Noise Output measurement | 39                                     |

| 28       | Figure 6-9 Module Compliance Board Power Supply Filters                                     | 40                                     |

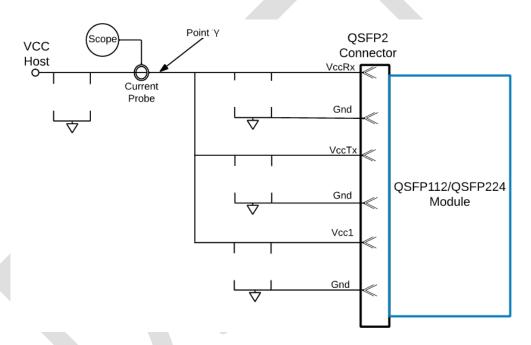

| 29       | Figure 6-10 Module Noise Output measurement                                                 | 40                                     |

| 30       | Figure 6-11 Module High Frequency Noise Tolerance                                           | 41                                     |

| 31       | Figure 6-12 Module Low Frequency Noise Tolerance                                            | 42                                     |

| 32       | Figure 6-13 Broadband Noise Tolerance Injection Probe Setup                                 | 43                                     |

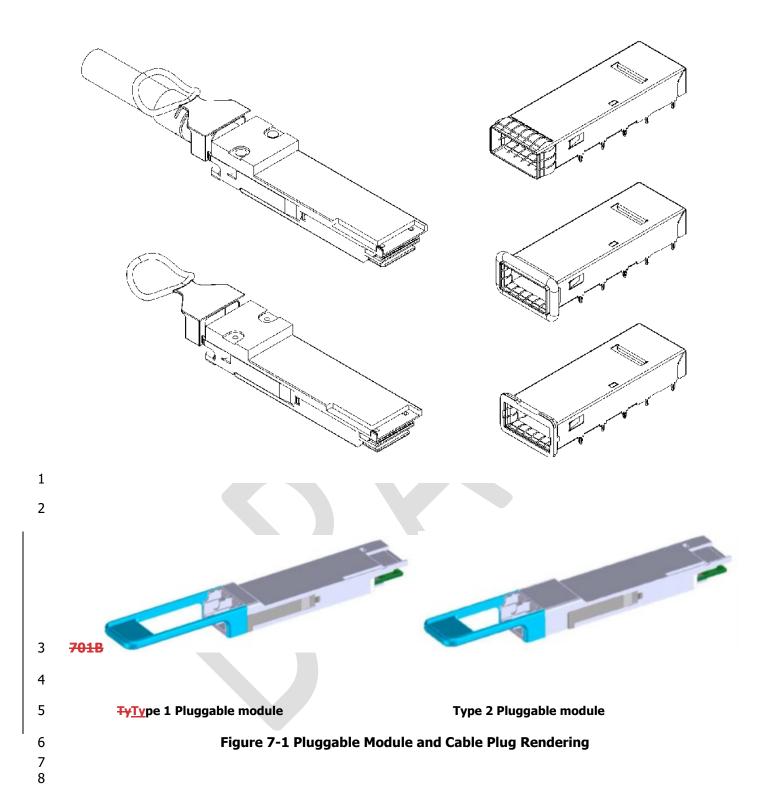

| 33       | Figure 7-1 Pluggable Module and Cable Plug Rendering                                        | <br>45                                 |

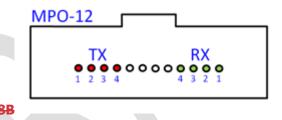

| 34       | Figure 7-2 Optical Receptacle and Lane Orientation for MPO connector                        | 47                                     |

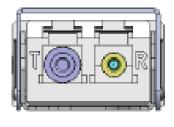

| 35       | Figure 7-3 Optical Receptacle for Dual LC Connector                                         | 47                                     |

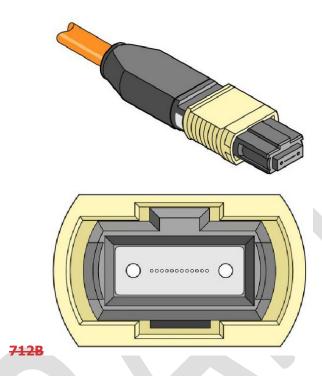

| 36       | Figure 7-4 MPO Optical Patch Cord                                                           | 48                                     |

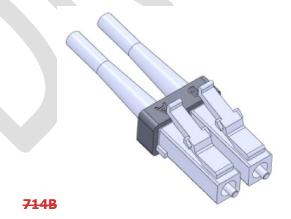

| 37       | Figure 7-5 Dual LC Optical Connector Plug                                                   | 48                                     |

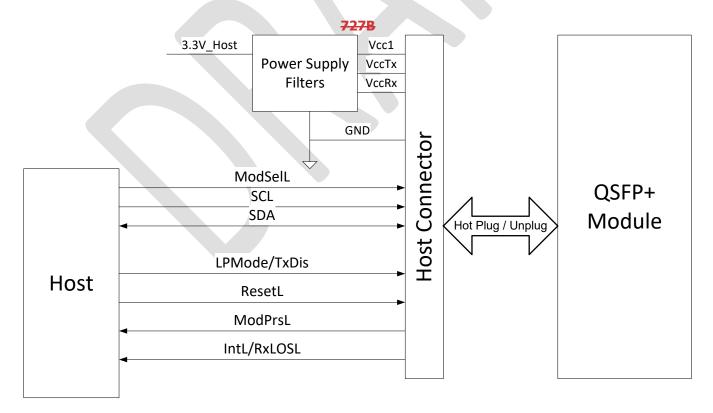

| 38       | Figure 9-1 Block diagram of module control signals                                          | 6<br>49                                |

| 39       | Figure A-1 Two-wire Interface Timing Diagram                                                | 54                                     |

| 40       | Figure 3-1 Plug and Receptacle Definition                                                   |                                        |

| 41       | Figure 4-1 Application reference model                                                      | <del>13</del>                          |

| 42       | Figure 5-1 Reference Points and Compliance Boards                                           |                                        |

| 43       | Figure 6-1 Module Pad Layout                                                                | —————————————————————————————————————— |

| 44       | Figure 6-2 Example: Host Board Schematic for Optical Modules                                |                                        |

| 45       | Figure 6-3 Example: Host Board Schematic for Passive Copper Cables                          |                                        |

|          | Figure 6-4 SDA/SCL options for pull-up resistor, bus capacitance and rise/fall times        |                                        |

| 46<br>47 | Figure 6-5 Recommended Host Board Power Supply Filtering                                    |                                        |

|          |                                                                                             |                                        |

| 48       | Figure 6-6 Example: Schematic of multiple QSFP+ power supply arrangement                    |                                        |

| 49       | Figure 6-7 QSFP+ Inrush Current Timing                                                      | <del>29</del>                          |

| 50       | Figure 6-8 Truncated Transfer Response for Host Board Power Supply Noise Output measurement |                                        |

| 51       | Figure 6-9 Module Compliance Board Power Supply Filters                                     | <del>32</del>                          |

| 52       | rigure o 10 module Noise Output measurement                                                 | 55                                     |

| 53       | Figure 6-11 Module High Frequency Noise Tolerance                                           | 34                                     |

| 1  | Figure 6-12 Module Low Frequency Noise Tolerance                                    | <del>35</del>  |

|----|-------------------------------------------------------------------------------------|----------------|

| 2  | Figure 6-13 Broadband Noise Tolerance Injection Probe Setup                         | <del>36</del>  |

| 3  | Figure 7-1 Pluggable Module and Cable Plug Rendering                                | 37             |

| 4  | Figure 7-2 Optical Receptacle and Lane Orientation for MPO connector                | 39             |

| 5  | Figure 7-3 Optical Receptacle for Dual LC Connector                                 | 39             |

| 6  | Figure 7-4 MPO Optical Patch Cord                                                   | <del>40</del>  |

| 7  | Figure 7-5 Dual LC Optical Connector Plug                                           | 40             |

| 8  | Figure 9-1 Block diagram of module control signals                                  | 41             |

| 9  | Figure A-1 Two-wire Interface Timing Diagram                                        | 46             |

| 10 | rigure ri z i rio i inio zinori uco riimi g ziugrani                                |                |

| 11 |                                                                                     |                |

| 12 | Tables                                                                              |                |

| 13 | Table 4-1 Example uses for QSFP+                                                    | 16             |

| 14 | Table 5-1 Reference Points                                                          | <br>17         |

| 15 | Table 6-1 Pad Function Definition                                                   | 20             |

| 16 | Table 6-2 Low Speed Electrical Specifications                                       | 25             |

| 17 | Table 6-3 QSFP+ Module Power Classes                                                | 31             |

| 18 | Table 6-4 Power Mode Control Bits in SFF-8636, Page 00h, Byte 93)                   | 31             |

| 19 | Table 6-5 Power Mode Truth Table                                                    | 32             |

| 20 | Table 6-6 QSFP+ Module Power Supply Specification                                   | 34             |

| 21 | Table 6-7 Truncated Filter Response Coefficients for Host Power Supply Noise Output | 38             |

| 22 | Table 8-1 Temperature Range Class of Operation                                      | 49             |

| 23 | Table 9-1 Control and Status Timing Requirements                                    | 50             |

| 24 | Table 9-2 QSFP+ Squelch and Tx/Rx Disable timing                                    | 53             |

| 25 | Table 4-1 Example uses for QSFP+                                                    | 13             |

| 26 | Table 5-1 Reference Points                                                          | <del>1</del> 4 |

| 27 | Table 6-1 Pad Function Definition                                                   | <del>16</del>  |

| 28 | Table 6-2 Low Speed Electrical Specifications                                       | 22             |

| 29 | Table 6-3 QSFP+ Module Power Classes                                                | <del>27</del>  |

| 30 | Table 6-4 Power Mode Control Bits in SFF-8636, Page 00h, Byte 93)                   | <del>27</del>  |

| 31 | Table 6-5 Power Mode Truth Table                                                    | <del>2</del> 8 |

| 32 | Table 6-6 QSFP+ Module Power Supply Specification                                   | <del>3</del> 0 |

| 33 | Table 6-7 Truncated Filter Response Coefficients for Host Power Supply Noise Output | 31             |

| 34 | Table 8-1 Temperature Range Class of Operation                                      | 41             |

| 35 | Table 9-1 Control and Status Timing Requirements                                    | 42             |

| 36 | Table 9-2 QSFP+ Squelch and Tx/Rx Disable timing                                    | 45             |

| 37 | Table A-3 Management interface timing parameters                                    | 47             |

| 38 |                                                                                     |                |

|    |                                                                                     |                |

**DRAFT** SFF-8679 Rev 1.8.54

# 1. Scope

1

8

9

10

11

13

2 This specification defines the electrical requirements for the QSFP10/14/28/56/112/224 pluggable 4-lane modules,

- 3 hereafter referred to as QSFP+/QSFP2. The scope includes electrical contacts for the host connector; status, control

- 4 and management interface signals; power supply requirements; fiber positions for optical interfaces; ESD and

- 5 thermal characteristics and color coding of pluggable QSFP+ modules and cables.

- 6 This specification supersedes and extends INF-8438 QSFP (Quad SFP) 4 Gb/s 4X Transceiver and SFF-8436 QSFP+

- 7 10 Gb/s 4X Pluggable Transceiver by supporting higher data rates.

# 2. References, Conventions, Keywords, Definitions

## 2.1 Industry Documents

The following documents are relevant to this specification:

```

12

- ANSI/TIA-568.3-ED Optical Fiber Cabling aAnd Components Standards

```

- CMIS Common Management Interface Specification

- 14 Environmental Test Methodology for Assessing the Performance of Electrical Connectors - EIA-364-1000 15 and Sockets Used in Controlled Environment Applications

- 16 - ESD specifications EN61000-4-2, JEDEC JESD22-A114-B

- NEBS<sup>TM</sup> Requirements: Physical Protection 17 - GR-63-CORE

- SONET Transport Systems: Common Criteria 18 - GR-253-CORE

- 19 - IEC 61754-7-1 Fibre optic interconnecting devices and passive components- Fibre optic connector 20

- interfaces Part 7-1 Type MPO connector family One fibre row

- 21 Fibre optic interconnecting devices and passive components- Fibre optic connector - IEC 61754-20

- 22 interfaces - Part 20 Type LC connector family

- 23 - IEEE Std 802.3 Standard for Ethernet

- 24 Standard for Ethernet, Amendment 4: Electrical interfaces based on 100 Gb/s signaling - IEEE Std 802.3ck

- 25 Draft Standard for Ethernet, Amendment: 200 Gb/s, 400 Gb/s, 800 Gb/s, and 1.6 Tb/s IEEE P802.3dj

- Fibre Channel- Physical Interface 6P (FC-PI-6P) 26 - INCITS 533-2016

- INCITS 534-2019 Information Technology Serial Attached SCSI 4 (SAS-4) 27

- 28 Fibre Channel- Physical Interface - 7P (FC-PI-7P) - INCITS 559

- 29 - INCITS 560 Fibre Channel – Physical Interfaces – 8 (FC-PI-8))

- 30 - INCITS 567-2023 Information Technology - Serial Attached SCSI - 4.1 (SAS-4.1)

- 31 - INF-8438 QSFP (Quad Small Formfactor Pluggable) Transceiver

- 32 - InfiniBand Architecture Specification

- 33 - ISO/IEC 14776-154: 2017 Information technology - Small computer system interface (SCSI) - Part 154: Serial 34 Attached SCSI-3 (SAS-3)

- 35 -Cross Reference to Select SFF Connectors - REF-TA-1011

- SFF Committee Cross Reference to Industry Products 36 - SFF-8024

- 37 - SFF-8436 OSFP+ 10 Gb/s 4X Pluggable Transceiver – (EIA-964)

- QSFP+ 10 Gb/s 4X Pluggable Transceiver Solution (QSFP10) 38 - SFF-8635

- 39 - SFF-8636 Management Interface for 4-Lane Modules

- 40 - SFF-8661 QSFP+ 28 Gb/s 4X Pluggable Module

- 41 - SFF-8662 QSFP+ 28 Gb/s 4X Connector (Style A)

- QSFP+ 28 Gb/s Cage (Style A) 42 - SFF-8663

- 43 - SFF-8665 QSFP+ 28 Gb/s 4X Pluggable Transceiver Solution (QSFP28)

- 44 - SFF-8672 QSFP+ 28 Gb/s 4X Connector (Style B)

- 45 - SFF-8682 QSFP+ 4X Connector (Style B)

- 46 - SFF-8683 QSFP+ Cage

- 47 - SFF-8685 OSFP+ 14 Gb/s 4X Pluggable Transceiver Solution (OSFP14)

- 48 - SFF-TA-1027 QSFP2 Cage, Connector and Module Specification

- 49 TIA-604-5 FOCIS 5 Fiber Optic Connector Intermateability Standard – Type MPO

- 50 - TIA-604-10 FOCIS 10 Fiber Optic Connector Intermateability Standard – Type LC

# 3

4

5

6 7

8

9

## 2.2 Technical References

1. "Measuring PSNR/PSRR/PSMR to meet QSFP/OSFP high-speed Requirements", Steve Sandler, Bob Tarasewicz, Pavel Zivny, Tony Ambrose, DesignCon 2023.

2. "Power Integrity Testing Requirements Introduce Extreme Interconnect Measures", Steve Sandler, Signal Integrity Journal, February 2023

https://www.signalintegrityjournal.com/articles/2981-power-integrity-testing-requirements-introduceextreme-interconnect-measures.

10 11

12 13

14

## 2.3 Sources

The complete list of SFF documents which have been published, are currently being worked on, or that have been expired by the SFF Committee can be found at https://www.snia.org/sff/specifications. Suggestions for improvement of this specification are welcome and should be submitted to https://www.snia.org/feedback.

15 16

Other standards may be obtained from the organizations listed below:

17 18

| Standard                                 | Organization                                                          | Website                                                                                                                |

|------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| ANSI/TIA                                 |                                                                       |                                                                                                                        |

| Electronic<br>Industry Alliance<br>(EIA) | Electronic Components Industry Association (ECIA)                     | https://www.ecianow.org/eia-technical-standards                                                                        |

| IEC                                      | International Electrotechnical Commission                             | https://webstore.iec.ch/                                                                                               |

| IEEE 802<br>standards                    | Institute of Electrical and Electronics Engineers (IEEE)              | https://ieeexplore.ieee.org/browse/standards/get-program/page/series?id=68                                             |

| INF                                      | SNIA                                                                  | https://www.snia.org/sff/specifications                                                                                |

| ISO                                      | International Organization for Standardization                        |                                                                                                                        |

| INCITS/Fibre<br>Channel                  | International Committee for<br>Information Technology<br>Standards    | https://webstore.ansi.org/sdo/incitsINCITS: Information_<br>Technology Industry Council (ansi.org) [webstore.ansi.org] |

| InfiniBand                               | InfiniBand Trade Association (IBTA)                                   | https://www.infinibandta.org                                                                                           |

| JEDEC                                    | Joint Electron Device<br>Engineering Council (JEDEC)                  | https://www.jedec.org                                                                                                  |

| OIF/CMIS                                 | Optical Internetworking Forum (OIF)_ Implementation Agreements        | https://www.oiforum.com/technical-work/implementation-agreements-ias/                                                  |

| PCIe                                     | PCI-SIG                                                               | http://pcisig.com                                                                                                      |

| SAS and other<br>ANSI standards          | International Committee for Information Technology Standards (INCITS) | https://www.incits.org                                                                                                 |

| Telcordia (GR documents)                 | Ericsson                                                              | https://telecom-info.njdepot.ericsson.net                                                                              |

#### 2.4 Conventions

The following conventions are used throughout this document:

**DEFINITIONS:** Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the definitions or in the text where they first appear.

**ORDER OF PRECEDENCE:** If a conflict arises between text, tables, or figures, the order of precedence to resolve the conflicts is text; then tables; and finally figures. Not all tables or figures are fully described in the text. Tables show data format and values.

**LISTS:** Lists sequenced by lowercase or uppercase letters show no ordering relationship between the listed items.

EXAMPLE 1 - The following list shows no relationship between the named items:

a.—red (i.e., one of the following colors):

A.—crimson; or

A. pink;

a.—blue; or

a. green.

Lists sequenced by numbers show an ordering relationship between the listed items.

EXAMPLE 2 - The following list shows an ordered relationship between the named items:

1.—top;

1.—middle; and

2.—bottom.

Lists are associated with an introductory paragraph or phrase and are numbered relative to that paragraph or phrase (i.e., all lists begin with an a. or 1. entry).

**DIMENSIONING CONVENTIONS**: The dimensioning conventions are described in ASME-Y14.5, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

**NUMBERING CONVENTIONS**: The ISO convention of numbering is used (i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point). This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

DRAFT SFF-8679 Rev 1.8.<u>5</u>4

# 3. Keywords, Acronyms, and Definitions

2 For the purposes of this document, the following keywords, acronyms, and definitions apply.

## 3.1 Keywords

**May:** Indicates flexibility of choice with no implied preference.

May or may not: Indicates flexibility of choice with no implied preference.

**Optional:** Describes features which are not required by the SFF specification. However, if any feature defined by the SFF specification is implemented, it shall be done in the same way as defined by the specification. Describing a feature as optional in the text is done to assist the reader.

**Prohibited:** Describes a feature, function, or coded value that is defined in a referenced specification to which this SFF specification makes a reference, where the use of said feature, function, or coded value is not allowed for implementations of this specification.

**Reserved:** Defines the signal on a connector contact. Its actual function is set aside for future standardization. It is not available for vendor specific use. Where this term is used for bits, bytes, fields, and code values; the bits, bytes, fields, and code values are set aside for future standardization. The default value shall be zero. The originator is required to define a Reserved field or bit as zero, but the receiver should not check Reserved fields or bits for zero.

**Restricted:** Refers to features, bits, bytes, words, and fields that are set aside for other standardization purposes (e.g., entities). If the context of the specification applies the restricted designation, then the restricted bit, byte, word, or field shall be treated as a value whose definition is not in scope of this document, and is not interpreted by this specification.

**Shall:** Indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products that conform to this specification.

**Should:** Indicates flexibility of choice with a strongly preferred alternative.

**Vendor specific:** Indicates something (e.g., a bit, field, code value) that is not defined by this specification. Specification of the referenced item is determined by the manufacturer and may be used differently in various implementations.

# 3.2 Acronyms and Abbreviations

The following acronyms may be used in this specification:

| ANSI | American National Standards Institute   |

|------|-----------------------------------------|

| ASIC | Application specific integrated circuit |

| ATM  | Asynchronous transfer mode              |

| CDR  | Clock and data recovery                 |

CML Current mode logic

**CORE** Central Office Relay Equipment

DDR Direct current

DDR Double data rate

EDR Extended data rate

EIA Electronic Industries Alliance

EMI Electromagnetic interference

**ESD** Electrostatic discharge

DRAFT SFF-8679 Rev 1.8.54

FC Fibre Channel

FDR Fourteen Gb/s Data Rate

Gb/s Gigabits per second

GbE Gigabit Ethernet

GFC Gigabit Fibre Channel

HDR High Data Rate

IECInternational Electrotechnical CommissionIEEEInstitute of Electrical and Electronics EngineersISOInternational Organization for StandardizationITUInternational Telecommunications UnionJEDECJoint Electron Device Engineering Council

**LVCMOS** Low voltage complementary metal oxide semiconductor

**LVTTL** Low voltage transistor-transistor logic

MPO Multi-fiber Push On Next Data Rate

**NEBS** Network Equipment Building System

**OC** Optical Carrier

OMA Optical Modulation Amplitude

PCB Printed circuit board

PI Physical Interface

QDR Quad Data Rate

QSFP Quad SFP

Rx Receiver

SAS Serial Attached SCSI

SDR Single Data Rate

SerDes Serializer-Deserializer

**SFP** Small Formfactor Pluggable

**SM** Single mode

SONET Synchronous Optical NETwork

STM Synchronous Transfer Mode

TIA Telecommunications Industry Association

TTL Transistor-transistor logic

Tx Transmitter

#### 3.3 Definitions

**Connector:** Each half of an interface that, when joined together, establishes electrical contact and mechanical retention between two components. In this specification, the term connector does not apply to any specific gender; it is used to describe the receptacle, the plug or the card edge, or the union of receptacle to plug or card edge. Other common terms include connector interface, mating interface, and separable interface.

**Contact mating sequence:** A term used to describe the order of electrical contact established/ terminated during mating/un-mating. Other terms include contact sequencing, contact positioning, mate first/break last, EMLB (early mate late break) staggered contacts, and long pin/short pin.

**Contacts:** A term used to describe connector terminals that make electrical connections across a separable interface.

**Module:** In this specification, module may refer to a plug assembly at the end of a copper (electrical) cable (passive or active), an active optical cable assembly, an optical transceiver, or a loopback.

**Plug:** A term used to describe the connector that contains the penetrating contacts of the connector interface as shown in Figure 3-1. Plugs typically contain stationary contacts. Other common terms include male, pin connector, and card edge.

**Receptacle:** A term used to describe the connector that contains the contacts that accept the plug contacts as shown in Figure 3-1. Receptacles typically contain spring contacts. Other common terms include female and socket connector.

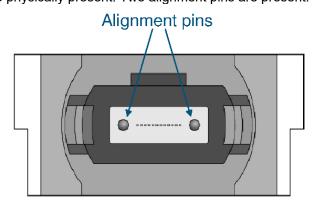

Figure 3-1 Plug and Receptacle Definition

## 4-3.

# **General Description**

# 4.1 Configuration Overview/Descriptions

- 3 This specification covers the following items:

- 4 Electrical specifications for QSFP+ modules including host connector contact assignments.

- Descriptions for data, control, status and management interface signals.

- 6 Power supply requirements.

- Electrostatic discharge (ESD) tolerance requirements.

- Color coding and labeling.

- 9 Fiber positions for optical interfaces.

- Environmental and thermal requirements (case temperatures).

- 11 Timing requirements.

- 12 This specification may be compatible with the example optical and electrical specifications in Table 4-1.

## 13

1

2

5

7

8

10

Table 4-1 Example uses for QSFP+

| ITU-T Recommendation G.957                      | STM-1, STM-4, STM-16                                               |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| Telcordia Technologies GR-253-CORE              | OC-3, OC-12, OC-48, OC-192                                         |  |  |  |

| IEEE Std 802.3                                  | 10 GbE, 25 GbE, 40 GbE, 50 GbE, 100 GbE, 200 GbE, 400_GbE, 800 GbE |  |  |  |

| InfinibandInfiniBand Architecture Specification | SDR, DDR, QDR, FDR, EDR, HDR, NDR                                  |  |  |  |

| Fibre Channel                                   | 8GFC, 16GFC, 32GFC, 128GFC, 256GFC                                 |  |  |  |

| Serial Attached SCSI                            | SAS-3, SAS-4; SAS-4.1                                              |  |  |  |

14 15

16

17

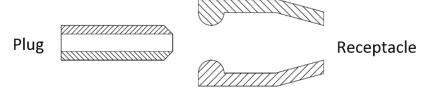

The Application Reference Model in Figure 4-1 shows the high-speed data interface between an ASIC (SerDes) and the module. Only one lane of the interface is shown for simplicity. Either parallel MPO or duplex LC fiber connectors can be used for the optical interface.

18

Figure 4-1 Application reference model

# Compliance boards and reference points

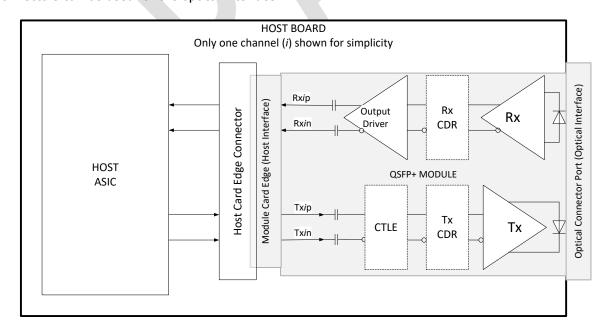

The module electrical interface test points are intended to be measured using compliance boards as shown in Figure 5-1. These compliance boards are intended to connect the module under test to test equipment for verification of compliance to the appropriate standard. The Module Compliance Board is used to test the module. The electrical parameters of the compliance boards should be specified by the appropriate standard. The Module Compliance Board and Host Compliance Board can be plugged together for calibration of compliance signals and to check the electrical parameters of the compliance boards. Reference points are described in Table 5-1.

Figure 5-1 Reference Points and Compliance Boards

Table 5-1 Reference Points

| rubico e recicione i cinco                                                                                                                                                 |                                                                                                                                                           |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Reference point                                                                                                                                                            | Description                                                                                                                                               |  |  |  |  |

| TP0                                                                                                                                                                        | Host ASIC transmitter output at ASIC package contact.                                                                                                     |  |  |  |  |

| TP1                                                                                                                                                                        | Input to Module Compliance Board. Used to test module input.                                                                                              |  |  |  |  |

| TP1a Host ASIC transmitter output through the host board and host card edge conductive output of the Host Compliance Board. Also used to calibrate module input compliance |                                                                                                                                                           |  |  |  |  |

| TP4                                                                                                                                                                        | Module output through the compliance board connectors at the output of the Module Compliance Board. Also used to calibrate host input compliance signals. |  |  |  |  |

| TP4a                                                                                                                                                                       | Input to Host Compliance Board. Used to test host input.                                                                                                  |  |  |  |  |

| TP5                                                                                                                                                                        | Input to host ASIC                                                                                                                                        |  |  |  |  |

| TP5a                                                                                                                                                                       | Far end module output through a reference channel                                                                                                         |  |  |  |  |

| Note: Individual standards may specify unique reference points                                                                                                             |                                                                                                                                                           |  |  |  |  |

8

10

DRAFT SFF-8679 Rev 1.8.<u>5</u>4

## <del>6.</del>3.

# **Electrical Specification**

This chapter contains pad definition data for the module. The pad definition data is generic for high speed datacom applications such as Fibre Channel, Ethernet and SONET/ATM. Reference points for high-speed electrical measurements are defined in Table 5-1 and illustrated in Figure 5-1. Reference points for all other electrical signals are at comparable points at the host card edge connector.

#### 6.1 Electrical Connector

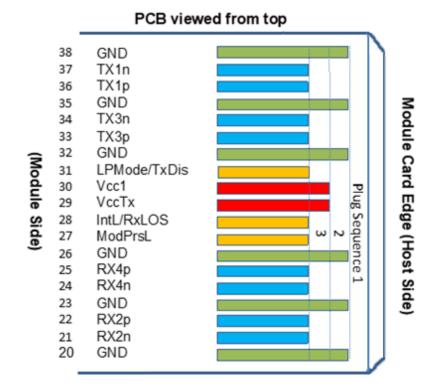

Figure 6-1 shows the signal symbols and pad numbering for the module edge connector. The diagram shows the module PCB edge as a top and bottom view, where bottom is nearer the host PCB. There are 38 pads intended for high speed signals, low speed signals, power and ground connections. Color green identifies ground pads, color red identifies power pads, color orange identifies low speed signal/control pads, and color blue identifies high speed I/O pads. Table 6-1 provides more information about each of the 38 pads.

The module contains a printed circuit board that mates with the electrical connector. The pads are designed for a sequenced mating:

15 Connected first, disconnected last: - ground contacts

16 Connected second, disconnected second: - power contacts

17 Connected third, disconnected first: - signal contacts

For EMI protection the signals to the connector should be shut off when the module is absent. Standard board layout practices such as connections to Vcc and GND with vias, the use of short and equal-length differential signal lines, and the use of microstrip-lines and 50  $\Omega$  terminations are recommended. The chassis ground (case common) of the module should be isolated from the module's circuit ground, GND, to provide the equipment designer flexibility regarding connections between external electromagnetic interference shields and circuit ground, GND, of the module.

QSFP+/QSFP28/QSFP112 Pads

Figure 6-1 Module Pad Layout

**Table 6-1 Pad Function Definition**

| Pad | Logic      | Symbol        | Description                                                                                       | Plug<br>Sequence | Note |

|-----|------------|---------------|---------------------------------------------------------------------------------------------------|------------------|------|

| 1   |            | GND           | Ground                                                                                            | 1                | 1    |

| 2   | CML-I      | Tx2n          | Transmitter Inverted Data Input                                                                   | 3                |      |

| 3   | CML-I      | Tx2p          | Transmitter Non-Inverted Data Input                                                               | 3                |      |

| 4   |            | GND           | Ground                                                                                            | 1                | 1    |

| 5   | CML-I      | Tx4n          | Transmitter Inverted Data Input                                                                   | 3                |      |

| 6   | CML-I      | Tx4p          | Transmitter Non-Inverted Data Input                                                               | 3                |      |

| 7   |            | GND           | Ground                                                                                            | 1                | 1    |

| 8   | LVTTL-I    | ModSelL       | Module Select                                                                                     | 3                |      |

| 9   | LVTTL-I    | ResetL        | Module Reset                                                                                      | 3                |      |

| 10  |            | VccRx         | +3.3V Power Supply Receiver                                                                       | 2                | 2    |

| 11  | LVCMOS-I/O | SCL           | Two-wire interface clock                                                                          | 3                |      |

| 12  | LVCMOS-I/O | SDA           | Two-wire interface data                                                                           | 3                |      |

| 13  |            | GND           | Ground                                                                                            | 1                | 1    |

| 14  | CML-O      | Rx3p          | Receiver Non-Inverted Data Output                                                                 | 3                |      |

| 15  | CML-O      | Rx3n          | Receiver Inverted Data Output                                                                     | 3                |      |

| 16  |            | GND           | Ground                                                                                            | 1                | 1    |

| 17  | CML-O      | Rx1p          | Receiver Non-Inverted Data Output                                                                 | 3                |      |

| 18  | CML-O      | Rx1n          | Receiver Inverted Data Output                                                                     | 3                |      |

| 19  |            | GND           | Ground 1                                                                                          |                  | 1    |

| 20  |            | GND           | Ground                                                                                            | 1                | 1    |

| 21  | CML-O      | Rx2n          | Receiver Inverted Data Output 3                                                                   |                  |      |

| 22  | CML-O      | Rx2p          | Receiver Non-Inverted Data Output 3                                                               |                  |      |

| 23  |            | GND           | Ground 1                                                                                          |                  | 1    |

| 24  | CML-O      | Rx4n          | Receiver Inverted Data Output 3                                                                   |                  |      |

| 25  | CML-O      | Rx4p          | Receiver Non-Inverted Data Output 3                                                               |                  |      |

| 26  |            | GND           | Ground                                                                                            | 1                | 1    |

| 27  | LVTTL-O    | ModPrsL       | Module Present                                                                                    | 3                |      |

| 28  | LVTTL-O    | IntL/RxLOSL   | Interrupt. Optionally configurable as RxLOSL via the management interface (SFF-8636 or CMIS).     | 3                |      |

| 29  |            | VccTx         | +3.3V Power supply transmitter                                                                    | 2                | 2    |

| 30  |            | Vcc1          | +3.3V Power supply                                                                                | 2                | 2    |

| 31  | LVTTL-I    | LPMode/TxD is | Low Power Mode. Optionally configurable as TxDis via the management interface (SFF-8636 or CMIS). | 3                |      |

| 32  |            | GND           | Ground                                                                                            | 1                | 1    |

| 33  | CML-I      | Tx3p          | Transmitter Non-Inverted Data Input                                                               | 3                |      |

| 34  | CML-I      | Tx3n          | Transmitter Inverted Data Input                                                                   | 3                |      |

| 35  |            | GND           | Ground                                                                                            | 1                | 1    |

| 36  | CML-I      | Tx1p          | Transmitter Non-Inverted Data Input 3                                                             |                  |      |

| 37  | CML-I      | Tx1n          | Transmitter Inverted Data Input 3                                                                 |                  |      |

| 38  |            | GND           | Ground 1 1                                                                                        |                  |      |

|     |            | 1.16 : 1      |                                                                                                   |                  | 1    |

Note 1: GND is the symbol for signal and supply (power) common for the module. All are common within the module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

For QSFP2, each connector GND contact is rated for a maximum current of 500 mA.

Note 2: VccRx, Vcc1 and VccTx are applied concurrently and may be internally connected within the module in any combination. Vcc contacts in SFF-8662 and SFF-8672 each have a steady state current rating of 1000 mA.

For QSFP2, each connector Vcc contact is rated for a maximum current of 1500 mA.

For Power Classes 4 and above the module differential loading of input voltage pads must not result in exceeding contact current limits.

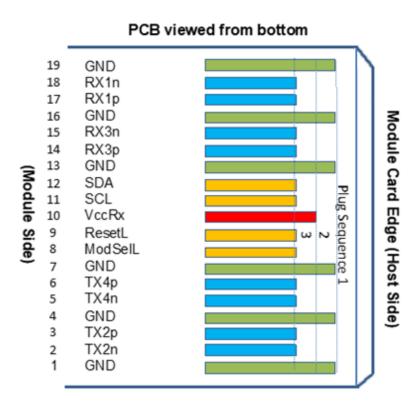

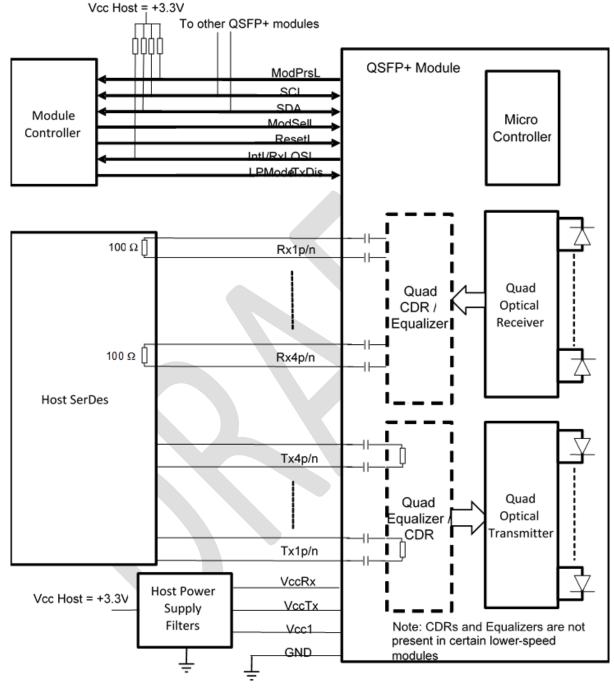

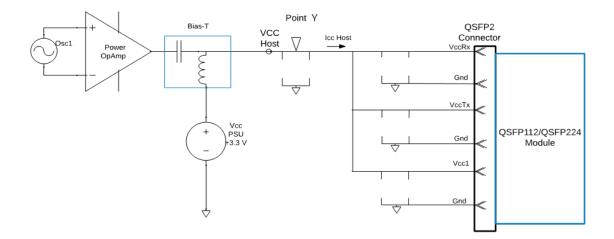

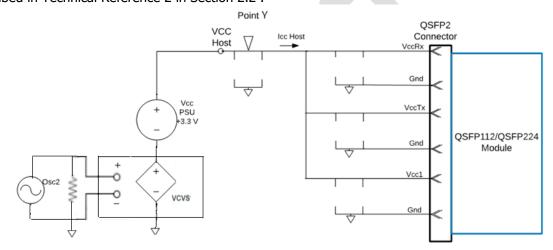

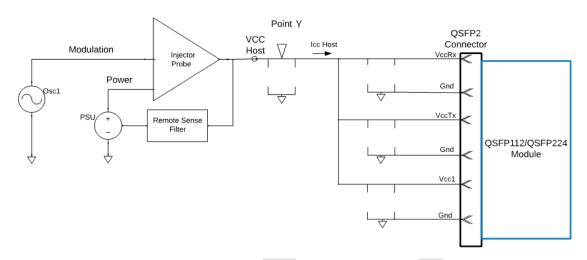

# **6.2 QSFP Example Circuits**

Figure 6-2 and Figure 6-3 provide example host board schematics for an optical QSFP+ module and for a QSFP+ copper cable plug respectively. Optical modules may have CDRs and equalizers in the module depending on the

application.

1

4

Figure 6-2 Example: Host Board Schematic for Optical Modules

6 7

**Figure 6-3 Example: Host Board Schematic for Passive Copper Cables**

DRAFT SFF-8679 Rev 1.8.54

## **6.3 Low Speed Signal Descriptions**

2 In addition to the two-wire interface the module has the following low speed signals for control and status:

- ModSelL

- ResetL

- LPMode/TxDis

- ModPrsL

- IntL/RxLOSL

7 8 9

1

3

4

5

6

The behavior of these signals is given in 6.3.1 to 6.3.5, the electrical specifications are in 6.4.1, and timing requirements are in 6.4.2 and Section 9. Timing requirements for the two-wire interface are in Appendix A.

10 11

12 **ModSelL** <del>1.1.1</del>6.3.1

13 ModSelL is an input signal. When held low by the host, the module responds to two-wire serial communication 14

- commands. The ModSelL signal allows the use of multiple modules on a single two-wire interface. When ModSelL

- 15 is high, the module shall not respond to or acknowledge any two-wire interface communication from the host. The

- 16 ModSelL signal input node shall be pulled towards Vcc in the module.

- In order to avoid conflicts, the host system shall not attempt two-wire interface communications within the ModSelL 17

- 18 hold time after any modules are deselected. Similarly, the host shall wait at least for the period of the ModSelL

- 19 setup time before communicating with the newly selected module. The assertion and de-assertion periods of

- 20 different modules may overlap as long as the above timing requirements are met.

21 <del>1.1.2</del>6.3.2 ResetL

- 22 The ResetL signal shall be pulled towards Vcc in the module. A low level on ResetL for longer than the minimum

- 23 pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default

- 24 state. Module Reset Assert Time (t\_init) starts on the rising edge after the low level of the ResetL pad is released.

- During the execution of a reset (t\_init) the host shall disregard all status bits until the module indicates a completion 25

- of reset interrupt by asserting "low" on the IntL/RxLOSL signal (see SFF-8636 or CMIS for details). However, on 26

- 27 power up (including hot insertion) the module should post this completion of reset interrupt without the host pulling

- 28 ResetL low.

29 <del>1.1.3</del>6.3.3 LPMode/TxDis

- 30 LPMode/TxDis is a dual-mode input signal from the host operating with active high logic. It shall be pulled towards

- Vcc in the module. At power-up or after reset, LPMode/TxDis behaves as LPMode. If supported, LPMode/TxDis can 31

- 32 be configured as TxDis using the two-wire interface. TxDis provides an optional fast mode, see definition in SFF-

- 8636 or CMIS. 33

- 34 When LPMode/TxDis is configured as LPMode, the module behaves as though TxDis=0.

- 35 By using the LPMode signal and a combination of the Power\_override, Power\_set and High\_Power\_Class\_Enable

- 36 software control bits (SFF-8636, Address A0h, Byte 93 bits 0,1,2), the host controls how much power a module can

- 37 consume. See CMIS Chapter 6.3.2 Module State Machine (MSM) on how LPMode is used in the control of the module

- power mode in transceivers with CMIS implementation. 38

- 39 See section 6.6 for more details on the power supply specifications.

- 40 When LPMode/TxDis is configured as TxDis, the module behaves as though LPMode=0. In this mode

- 41 LPMode/TxDis when set to 1 or 0 disables or enables all optical transmitters within the times specified in Table 9-1.

- 42 Changing LPMode/TxDis mode from LPMode to TxDis when the LPMode/TxDis state is high disables all optical

- 43 transmitters. If the module was in low power mode, then the module transitions out of low power mode at the

- same time. If the module is already in high power state (Power Override control bits) with transmitters already 44

DRAFT SFF-8679 Rev 1.8.<u>5</u>4

- 1 enabled, the module shall disable all optical transmitters.

- 2 Changing the LPMode/TxDis mode from LPMode to TxDis when the LPMode/TxDis state is low, simply changes the

- 3 behavior of the mode of LPMode/TxDis. The behavior of the module depends on the Power Override control bits.

- 4 Timing requirements for LPMode/TxDis mode changes are found in Table 9-1-.

- Note that the "soft" functions of TxDis, LPMode, IntL and RxLOSL allow the host to poll or set these values over

- 6 the two-wire interface as an alternative to monitoring/setting signal values. Asserting either the "hard pin" or "soft

- 7 bit" (or both) for TxDis or LPMode results in that function being asserted.

- 8 <del>1.1.46.3.4</del> ModPrsL

- 9 ModPrsL is pulled up towards VccHost on the host board and pulled towards ground in the module. ModPrsL is

- 10 pulled low when the module is inserted and released to high when the module is physically absent from the host

- 11 connector.

- 12 **1.1.5**6.3.5 IntL/RxLOSL

- 13 IntL/RxLOSL is a dual-mode active-low, open-collector output signal from the module. It shall be pulled up towards

- 14 Vcc on the host board. At power-up or after ResetL is released to high, IntL/RxLOSL is configured as IntL. If

- 15 supported, IntL/RxLOSL can be optionally programmed as RxLOSL using the two-wire interface. Rx LOS and RxLOSL

- timings, including an optional fast mode, are given in Table 9-1.

- 17 If IntL/RxLOSL is configured as IntL, a low indicates a change in module state, possible module operational

- fault or a module condition that sets an unmasked flag as defined in SFF-8636 or CMIS. The source of the

- 19 IntL "low" can be read, cleared or masked using the two-wire interface. If the interrupt was after a

- 20 module reset and SFF-8636, Page 00h, Byte 2, bit 0 (Data Not Ready bit) is 0, then the module releases

- 21 IntL to high after the host has read the Data Not Ready bit. For all other interrupt causes, the module

- 22 releases IntL to high after the host has read the flag associated with the cause of the interrupt.

- 23 If IntL/RxLOSL is configured as RxLOSL, a low indicates that there is a loss of received optical power on

- 24 at least one lane. "high" indicates that there is no loss of received optical power. Rx LOS and RxLOSL

- 25 timings, including an optional fast mode, are given in Table 9-1. The actual condition of loss of optical

- 26 receive power is specified by other governing documents. The module shall pull RxLOSL to low if any lane

- 27 in a multiple lane module or cable has a LOS condition and shall release RxLOSL to high only if no lane

- 28 has a LOS condition.

- 29 Timing requirements for IntL/RxLOSL mode change are found in Table 9-1. If the module has no interrupt flags

- 30 asserted (IntL/RxLOSL is high), there should be no change in IntL/RxLOSL states after the mode change.

# 6.4 Low Speed Signal Electrical Specifications

- 32 **1.2.1**6.4.1 Low Speed Signaling

- Low speed signaling other than SCL and SDA is based on Low Voltage TTL (LVTTL) operating at Vcc. Vcc refers to

- 34 the generic supply voltages of VccTx, VccRx, VccHost or Vcc1. Hosts shall use a pull-up toward VccHost on each of

- 35 the two-wire interface SCL (clock) and SDA (data), and on the two low speed module status outputs ModPrsL and

- 36 IntL/RxLOSL.

- 37 The SCL and SDA is a hot plug interface that may support a bus topology. During module insertion or removal, the

- 38 module may implement a pre-charge circuit which prevents corrupting data transfers from other modules that are

- 39 already using the bus.

- 40 Compliance with Table 6-2 provides compatibility between host bus masters and the two-wire interface.

**Table 6-2 Low Speed Electrical Specifications**

| Parameter                 | Symbol | Min     | Max       | Unit | Notes/Conditions                        |

|---------------------------|--------|---------|-----------|------|-----------------------------------------|

| SCL and SDA               | VOL    | 0       | 0.4       | V    | IOL(max)=3 mA                           |

|                           |        |         |           |      | IOL(max)=20 mA for Fast-                |

|                           |        |         |           |      | mode pplus                              |

|                           | VOH    | Vcc-0.5 | Vcc+0.3   | V    |                                         |

| SCL and SDA               | VIL    | -0.3    | Vcc*0.3   | V    |                                         |

|                           | VIH    | Vcc*0.7 | Vcc + 0.5 | V    |                                         |

| Capacitance on SCL and    | Ci     |         | 14        | pF   | Looking into the module SCL and SDA     |

| SDA I/O contact.          |        |         |           |      | contacts.                               |

| Total bus capacitive load | Cb     |         | 100       | pF   | For 400 kHz clock rate use_——3 kΩ       |

| for SCL and SDA for up    |        |         |           |      | pullup resistor, max                    |

| to 400 kHz SCL rate       |        |         |           |      | For 1000_kHz clock rate refer to Figure |

| (includes capacitance of  |        |         |           |      | 6-4                                     |

| all elements on the bus). |        |         | 200       | pF   | For 400 kHz clock rate use_             |

|                           |        |         |           |      | 1.6 kΩ pullup resistor, max             |

|                           |        |         |           |      | For 1000 kHz clock rate refer to Figure |

|                           |        |         |           |      | 6-4                                     |

| LPMode/TxDis, ResetL      | VIL    | -0.3    | 0.8       | V    |                                         |

| and ModSelL               | VIH    | 2       | Vcc+0.3   | V    |                                         |

|                           | Iin    | -365    | 125       | μA   | 0 V ≤ Vin ≤ Vcc                         |