SFF specifications are available at http://www.snia.org/sff/specifications.

SFF-9400

Reference Guide for

Universal 4/8X Pinouts

Rev 1.0

July 18, 2018

Secretariat: SFF TA TWG

Abstract: This specification outlines a set of connector pin signal definitions for an internal cable interface. The definitions are not functionally compatible but do prevent physical damage. Possible applications include, but are not limited to, SAS-3 and SAS-4.

This specification provides a common reference for systems manufacturers, system integrators, and suppliers.

This specification is made available for public review, and written comments are solicited from readers. Comments received by the members will be considered for inclusion in future revisions of this specification.

The description of a connector in this specification does not assure that the specific component is actually available from connector suppliers. If such a connector is supplied it must comply with this specification to achieve interoperability between suppliers.

POINTS OF CONTACT:

Barry Olawsky Hewlett Packard 11445 Compaq Center Drive West Houston, TX 77070

Ph: 281-514-8624

Email: barry.olawsky@hp.com

Chairman SFF TA TWG

Email: SFF-Chair@snia.org

## **Intellectual Property**

The user's attention is called to the possibility that implementation of this Specification may require the use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith. This specification is considered SNIA Architecture and is covered by the SNIA IP Policy and as a result goes through a request for disclosure when it is published. Additional information can be found at the following locations:

- Results of IP Disclosures: <a href="http://www.snia.org/sffdisclosures">http://www.snia.org/sffdisclosures</a>

- SNIA IP Policy: <a href="http://www.snia.org/ippolicy">http://www.snia.org/ippolicy</a>

## **Change History**

Rev 0.2

- No change history information available before this release

Rev 1.0 (July 18, 2018)

- Upgraded to SNIA template format

- Changed header from "Reference Guide" to "Published"

- Added "Reference" watermark

- Removed Section 1.1 Application Specific Criteria

- Added references

- Minor editorial changes

#### Foreword

The development work on this specification was done by the SNIA SFF TWG, an industry group. Since its formation as the SFF Committee in August 1990, the membership has included a mix of companies which are leaders across the industry.

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type, connector location, between vendors. The SFF Committee provided a forum for system integrators and vendors to define the form factor of disk drives.

During their definition, other activities were suggested because participants in SFF faced more challenges than the form factors. In November 1992, the charter was expanded to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

In July 2016, the SFF Committee transitioned to SNIA (Storage Networking Industry Association), as a TA (Technology Affiliate) TWG (Technical Work Group).

Industry consensus is not a requirement to publish a specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

SFF meets during the T10 (see <a href="www.t10.org">www.t10.org</a>) and T11 (see <a href="www.t11.org">www.t11.org</a>) weeks, and SSWGs (Specific Subject Working Groups) are held at the convenience of the participants.

Many of the specifications developed by SFF have either been incorporated into standards or adopted as standards by ANSI, EIA, JEDEC and SAE.

For those who wish to participate in the activities of the SFF TWG, the signup for membership can be found at:

http://www.snia.org/sff/join

The complete list of SFF Specifications which have been completed or are currently being worked on by the SFF Committee can be found at:

http://www.snia.org/sff/specifications

Suggestions for improvement of this specification will be welcome, they should be submitted to:

http://www.snia.org/feedback

# **CONTENTS**

| 1.  | Scope   |                                |                   |             | 5          |

|-----|---------|--------------------------------|-------------------|-------------|------------|

|     | 1.1     | Application Specific Criteria  | Error!            | Bookmark no | t defined. |

|     | 1.2     | Copyright                      |                   |             | 5          |

|     | 1.3     |                                |                   |             | 5          |

| 2.  | Refer   | ences                          |                   |             | 6          |

|     | 2.1     | Industry Documents             |                   |             | 6          |

|     | 2.2     | Sources                        |                   |             | 6          |

|     |         | Conventions                    |                   |             | 6          |

|     | 2.4     | Definitions                    |                   |             | 6          |

| 3.  | Gener   | al Description                 |                   |             | 7          |

|     | 3.1     | Type 1 4X Pinout               |                   |             | 7          |

|     | 3.2     | Type 2 4X Pinout               |                   |             | 7          |

|     |         | Type 3 4X Pinout               |                   |             | 8          |

|     |         | Type 1 8X Pinout               |                   |             | 8          |

|     |         | Type 2 8X Pinout               |                   |             | 3          |

|     | 3.6     | Type 3 8X Pinout               |                   |             | C          |

|     |         |                                |                   |             |            |

|     |         |                                | FIGURES           |             |            |

|     |         | 1: Location of Vendor Specific |                   |             | 7          |

|     |         | 2: Location of Vendor Specific | Pins in 8X Pinout |             | 7          |

| -   |         | 3: Type 1 4X pinout            |                   |             | 7          |

|     |         | 4: Type 2 4X Pinout            |                   |             | 7          |

|     |         | 5: Type 3 4X Pinout            |                   |             | 8          |

|     |         | 6: Type 1 8X Pinout            |                   |             | 8          |

|     |         | 7: Type 2 8X Pinout            |                   |             | 8          |

| -10 | nure X- | 8. Type 3 8X Pinout            |                   |             | }          |

### 1. Scope

This reference guide outlines a set of connector pin signal definitions for a two-row internal cable connector interface. The definitions are not functionally compatible but do prevent physical damage when two different pinout options are mated. Possible applications include, but are not limited to, SAS-3 and SAS-4. The intent is to facilitate greater flexibility and increased usage.

## 1.1 Copyright

The SNIA hereby grants permission for individuals to use this document for personal use only, and for corporations and other business entities to use this document for internal use only (including internal copying, distribution, and display) provided that:

- 1. Any text, diagram, chart, table or definition reproduced shall be reproduced in its entirety with no alteration, and,

- 2. Any document, printed or electronic, in which material from this document (or any portion hereof) is reproduced shall acknowledge the SNIA copyright on that material, and shall credit the SNIA for granting permission for its reuse.

Other than as explicitly provided above, there may be no commercial use of this document, or sale of any part, or this entire document, or distribution of this document to third parties. All rights not explicitly granted are expressly reserved to SNIA.

Permission to use this document for purposes other than those enumerated (Exception) above may be requested by e-mailing copyright\_request@snia.org. Please include the identity of the requesting individual and/or company and a brief description of the purpose, nature, and scope of the requested use. Permission for the Exception shall not be unreasonably withheld. It can be assumed permission is granted if the Exception request is not acknowledged within ten (10) business days of SNIA's receipt. Any denial of permission for the Exception shall include an explanation of such refusal.

## 1.2 Disclaimer

The information contained in this publication is subject to change without notice. The SNIA makes no warranty of any kind with regard to this specification, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The SNIA shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this specification.

Suggestions for revisions should be directed to http://www.snia.org/feedback/.

#### 2. References

#### 2.1 Industry Documents

- INCITS 519 Serial Attached SCSI 3 (SAS-3)

- INCITS 534 Serial Attached SCSI 4 (SAS-4)

#### 2.2 Sources

There are several projects active within the SFF TWG. The complete list of specifications which have been completed or are still being worked on is contained in the document SFF-8000 which can be found at <a href="http://www.snia.org/sff/specifications">http://www.snia.org/sff/specifications</a>.

Copies of ANSI standards may be purchased from the InterNational Committee for Information Technology Standards (<a href="http://www.techstreet.com/incitsgate.tmpl">http://www.techstreet.com/incitsgate.tmpl</a>).

#### 2.3 Conventions

The dimensioning conventions are described in ANSI-Y14.5M, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

The ISO convention of numbering is used i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point. This is equivalent to the English/American convention of a comma and a period.

| American    | F     | rench |       | ISO   |

|-------------|-------|-------|-------|-------|

| 0.6         |       | 0,6   |       | 0.6   |

| 1,000       | 1     | 000   | 1     | 000   |

| 1,323,462.9 | 1 323 | 462,9 | 1 323 | 462.9 |

### 2.4 Definitions

GND: Signal return pin sometimes referred to as a ground

**HS:** High speed differential pair signal pin

**Optional:** This term describes features which are not required by the SFF Specification. However, if any feature defined by the SFF Specification is implemented, it shall be done in the same way as defined by the Specification. Describing a feature as optional in the text is done to assist the reader. If there is a conflict between text and tables on a feature described as optional, the table shall be accepted as being correct.

SB: Sideband signal pin

**Vendor Specific:** This term is used the signal on a connector pin and its actual function is determined by each vendor and not reserved for future standardization.

## 3. General Description

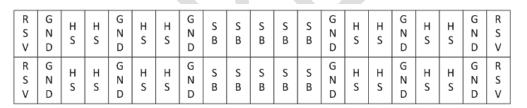

Both 4X and 8X pinouts include a combination of high speed differential pairs and vendor specific signals. Figure 3-1and Figure 3-2 illustrate the location of vendor specific pins for 4X and 8X connector pinouts respectively. Each vendor specific block consists of ten pins.

| R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | VENDOR   | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V |

|-------------|-------------|--------|--------|-------------|--------|--------|-------------|----------|-------------|--------|--------|-------------|--------|--------|-------------|-------------|

| R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | SPECIFIC | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V |

FIGURE 3-1: LOCATION OF VENDOR SPECIFIC PINS IN A 4X PINOUT

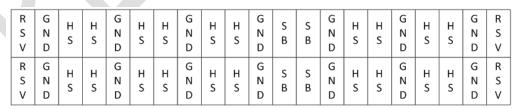

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | VENDOR   | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | VENDOR   | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

|-------------|--------|--------|-------------|--------|--------|-------------|----------|-------------|--------|--------|-------------|--------|--------|-------------|-------------|-------------|-------------|--------|--------|-------------|--------|--------|-------------|----------|-------------|--------|--------|-------------|--------|--------|-------------|

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | SPECIFIC | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | SPECIFIC | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

FIGURE 3-2: LOCATION OF VENDOR SPECIFIC PINS IN 8X PINOUT

## 3.1 Type 1 4X Pinout

The Type 1 4X Pinout assigns all vendor specific pins as discrete sideband signals as shown in Figure 3-3.

FIGURE 3-3: TYPE 1 4X PINOUT

## 3.2 Type 2 4X Pinout

The Type 2 4X Pinout assigns seven vendor specific pins as discrete sideband signals and three for an additional high-speed differential pair as shown in Figure 3-4.

FIGURE 3-4: TYPE 2 4X PINOUT

## 3.3 Type 3 4X Pinout

The Type 3 4X Pinout assigns all vendor specific pins for high-speed differential pairs as shown in Figure 3-5.

| R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V |

|-------------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|-------------|

| R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V |

FIGURE 3-5: TYPE 3 4X PINOUT

## 3.4 Type 1 8X Pinout

The Type 1 8X Pinout assigns all vendor specific pins as discrete sideband signals as shown in Figure 3-6.

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | S<br>B | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | S<br>B | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|--------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|-------------|-------------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|--------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | S<br>B | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | S<br>B | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

FIGURE 3-6: TYPE 1 8X PINOUT

## 3.5 Type 2 8X Pinout

The Type 2 8X Pinout assigns fourteen vendor specific pins as discrete sideband signals and two additional high-speed differential pairs as shown in Figure 3-7.

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|-------------|-------------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | R<br>S<br>V | R<br>S<br>V | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | S<br>B | S<br>B | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

FIGURE 3-7: TYPE 2 8X PINOUT

## 3.6 Type 3 8X Pinout

The Type 3 8X Pinout assigns all vendor specific pins for high-speed differential pairs as shown in Figure 3-8.

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|--------|--------|-------------|

| G<br>N<br>D | H<br>S | H<br>S | G<br>N<br>D |

FIGURE 3-8: TYPE 3 8X PINOUT