SFF specifications are available at http://www.snia.org/sff/specifications or ftp://ftp.seagate.com/sff

This specification was developed by the SFF Committee prior to it becoming the SFF TA (Technology Affiliate) TWG (Technical Working Group) of SNIA (Storage Networking Industry Association).

The information below should be used instead of the equivalent herein.

POINTS OF CONTACT:

Chairman SFF TA TWG Email: SFF-Chair@snia.org

If you are interested in participating in the activities of the SFF TWG, the membership application can be found at:

http://www.snia.org/sff/join

The complete list of SFF Specifications which have been completed or are currently being worked on can be found at:

http://www.snia.org/sff/specifications/SFF-8000.TXT

The operations which complement the SNIA's TWG Policies & Procedures to guide the SFF TWG can be found at:

http://www.snia.org/sff/specifications/SFF-8032.PDF

Suggestions for improvement of this specification will be welcome, they should be submitted to:

http://www.snia.org/feedback

SFF Committee documentation may be purchased in hard copy or electronic form SFF specifications are available at ftp://ftp.seagate.com/sff

#### SFF Committee

INF-8479i Specification for

#### POP4 Four Channel Pluggable Optical Transceiver

Rev 1.0 September 4 2002

Secretariat: SFF Committee

Abstract: This specification describes the POP4 Four Channel (parallel optic) Pluggable Optical transceiver. It was developed by the MSA (Multiple Source Agreement) group in which the following companies participated:

Agilent Technologies Emcore OptolC Technology Primarion Zarlink

This Information Specification was not developed or endorsed by the SFF Committee but was submitted for distribution on the basis that it is of interest to the storage industry. The copyright on the contents remains with the contributor.

Contributors are not required to abide by the SFF patent policy. Readers are advised of the possibility that there may be patent issues associated with an implementation which relies upon the contents of an 'i' specification.

SFF accepts no responsibility for the validity of the contents.

#### POINTS OF CONTACT:

Dan Rausch Technical Editor Avago Technologies 350 West Trimble Rd San Jose CA 95131

408-435-6689 dan.rausch@avagotech.com

I. Dal Allan Chairman SFF Committee 14426 Black Walnut Court Saratoga CA 95070

408-867-6630 endlcom@acm.org

#### EXPRESSION OF SUPPORT BY MANUFACTURERS

The following member companies of the SFF Committee voted in favor of this industry specification.

The following member companies of the SFF Committee voted against this industry specification.

The following member companies of the SFF Committee voted to abstain on this industry specification.

#### SFF COMMITTEE

The SFF Committee is an industry group. The membership of the committee since its formation in August 1990 has included a mix of companies which are leaders across the industry.

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type, connector location, between vendors.

The first use of these disk drives was in specific applications such as laptop portable computers and system integrators worked individually with vendors to develop the packaging. The result was wide diversity, and incompatibility.

The problems faced by integrators, device suppliers, and component suppliers led to the formation of the SFF Committee as an industry ad hoc group to address the marketing and engineering considerations of the emerging new technology.

During the development of the form factor definitions, other activities were suggested because participants in the SFF Committee faced more problems than the physical form factors of disk drives. In November 1992, the charter was expanded to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

Those companies which have agreed to support a specification are identified in the first pages of each SFF Specification. Industry consensus is not an essential requirement to publish an SFF Specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

SFF Committee meetings are held during T10 weeks (see www.t10.org), and Specific Subject Working Groups are held at the convenience of the participants. Material presented at SFF Committee meetings becomes public domain, and there are no restrictions on the open mailing of material presented at committee meetings.

Most of the specifications developed by the SFF Committee have either been incorporated into standards or adopted as standards by EIA (Electronic Industries Association), ANSI (American National Standards Institute) and IEC (International Electrotechnical Commission).

Suggestions for improvement of this specification will be welcome. They should be sent to the SFF Committee, 14426 Black Walnut Ct, Saratoga, CA 95070.

The complete list of SFF Specifications which have been completed or are currently being worked on by the SFF Committee can be found at:

ftp://ftp.seagate.com/sff/SFF-8000.TXT

If you wish to know more about the SFF Committee, the principles which guide the activities can be found at:

ftp://ftp.seagate.com/sff/SFF-8032.TXT

If you are interested in participating or wish to follow the activities of the SFF Committee, the signup for membership and/or documentation can be found at:

www.sffcommittee.com/ie/join.html

or the following application can be submitted.

| Name:    | Title:                             |                      |          |       |                  |  |  |  |

|----------|------------------------------------|----------------------|----------|-------|------------------|--|--|--|

| Company: |                                    |                      |          |       |                  |  |  |  |

| Address: |                                    |                      |          |       |                  |  |  |  |

|          |                                    |                      |          |       |                  |  |  |  |

| Phone:   |                                    | Fax:                 |          |       |                  |  |  |  |

| Email:   |                                    |                      |          |       |                  |  |  |  |

| Please   | register me with the SFF Co        | ommittee for one yea | ır.      |       |                  |  |  |  |

| Vot      | ting Membership w/Electronic       | c documentation      | \$ 2     | 2,160 |                  |  |  |  |

| Vot      | ting Membership w/Meeting do       | ocumentation         | \$ 1     | ,800  |                  |  |  |  |

| Nor      | n-voting Observer w/Electron       | nic documentation    | \$<br>\$ |       | U.S.<br>Overseas |  |  |  |

| Nor      | n-voting Observer w/Meeting        | documentation        |          |       | U.S.<br>Overseas |  |  |  |

| Check I  | Payable to SFF Committee for       | r \$ is Encl         | .osed    |       |                  |  |  |  |

| Please   | invoice me for \$                  | on PO #:             |          |       |                  |  |  |  |

| MC/Visa  | a/AmX                              | Ex                   | pires    | s     |                  |  |  |  |

| 144      | F Committee<br>126 Black Walnut Ct | 408-867-663          | 0        |       |                  |  |  |  |

| Sar      | ratoga CA 95070                    | endlcom@acm          | ı.org    |       |                  |  |  |  |

# Four Channel Pluggable Optical Transceiver Multi-Source Agreement

### **POP4 MSA**

# Technical Specification Revision 1.0

This MSA provides a common specification for 4-channel pluggable, parallel optic transceivers with data rates up to 2.7Gbps per channel. The technical specification defines the package outline, front panel cutout, printed circuit board footprint, electrical and optical interface and general performance characteristics. It is intended for public use by Networking Equipment Manufacturers, system integrators and component vendors alike.

Features of the pluggable 4 channel transceiver parallel fiber optic modules defined by this document include:

- 4 Transmit Channels and 4 Receive Channels

- 1 to 2.7 GBd (per channel) Signal Rate

- Data I/O is CML compatible with DC blocking capacitors

- Link length up to 300 m with 50/125 μm, 500 MHz•km multi-mode fiber at 2.5 Gbps

- Channel BER 10<sup>-12</sup>

- Standard MTP<sup>TM</sup>(MPO) ribbon fiber connector interface

- Pluggable MegArray™ ball grid array connector

This specification and additional information are available at:

www.popoptics.org

#### POP4 MSA

# **Table of contents**

|                   | age Outline                                                               |    |

|-------------------|---------------------------------------------------------------------------|----|

|                   | it Board Footprint                                                        |    |

|                   | Frontplate Layout for Panel Accessed Modules                              |    |

|                   | sceiver Module Signals                                                    |    |

|                   | Franceiver Pad Assignments                                                |    |

|                   | Fransceiver MTP Connector                                                 |    |

| 5 Defin           | itions: Signals, Pad Functions, Posts                                     | 7  |

|                   | sceiver Specifications                                                    |    |

|                   | General Specifications                                                    |    |

|                   | Fransmitter Specifications                                                |    |

| 6.3 I             | Receiver Specifications                                                   | 10 |

|                   | Fiming Requirements of Control and Status Signals                         |    |

|                   | ink Length                                                                |    |

| 6.5.1             |                                                                           |    |

| 6.5.2<br>7 Eve \$ | Restricted Launch (Optional)                                              |    |

|                   |                                                                           |    |

|                   | Figures                                                                   |    |

| Figure 1          | Module layout                                                             | 3  |

| Figure 2          | Host circuit board footprint layout                                       | 4  |

| Figure 3          | Host frontplate layout                                                    |    |

| Figure 4          | Recommended power supply filter network for both transmitter and receiver |    |

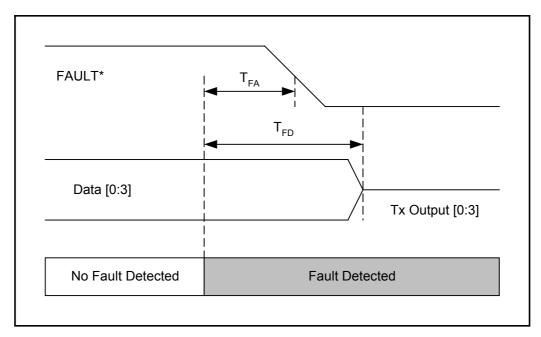

| Figure 5          | Transmitter FAULT* signal timing diagram                                  |    |

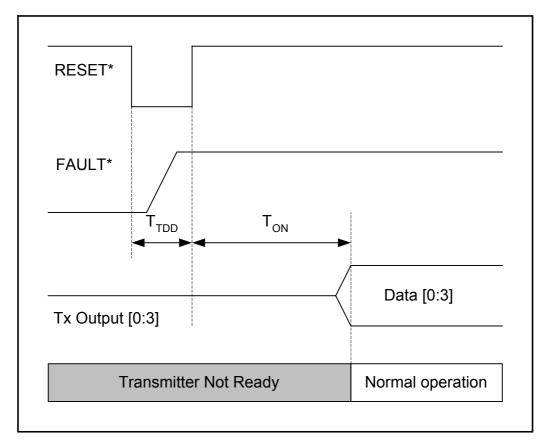

| Figure 6          | Transmitter RESET* signal timing diagram                                  |    |

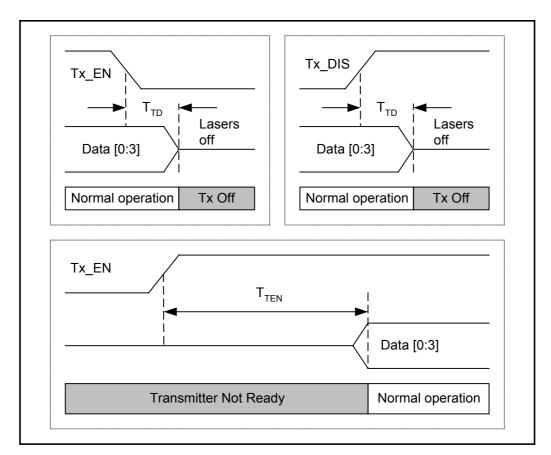

| Figure 7          | Transmitter ENABLE and DISABLE signal timing diagram                      |    |

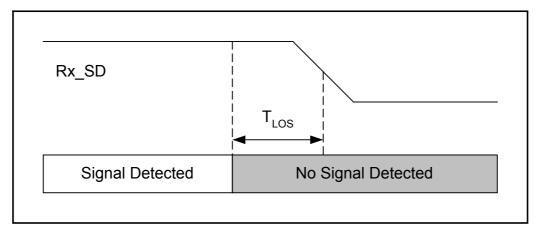

| Figure 8          | Receiver Signal Detect timing diagram                                     |    |

| Figure 9          | Receiver ENABLE signal timing diagram                                     | 13 |

| List of           | Tables                                                                    |    |

| Table 1           | Module dimensions                                                         |    |

| Table 2           | Host circuit board footprint mechanical dimensions                        |    |

| Table 3           | Host frontplate dimensions                                                |    |

| Table 4           | Transceiver module pad assignment                                         |    |

| Table 5           | Timing requirements of control and status signals                         | 13 |

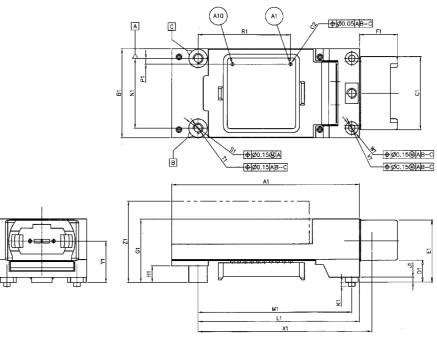

# 1 Package Outline

Tolerancing per ASME Y-14.5-1994. All dimensions are in millimeters.

Figure 1 Module layout

Table 1 Module dimensions

| Key | Dimension<br>[mm] | Tolerance<br>[mm] | Comments                                                             |

|-----|-------------------|-------------------|----------------------------------------------------------------------|

| A1  | 42.67             | MAX               | Length of module body, less optical receptacle assembly              |

| B1  | 18.00             | MAX               | Width of module body                                                 |

| C1  | 15.25             | MAX               | Width of optical receptacle assembly                                 |

| D1  | 2.70              | MIN               | Height of bottom of optical receptacle assembly                      |

| E1  | 15.70             | MAX               | Height of top of optical receptacle assembly                         |

| F1  | 7.40              | MIN               | Length of optical receptacle assembly                                |

|     | 10.00             | MAX               |                                                                      |

| G1  | 15.55             | MAX               | Height of top of module                                              |

| H1  | 3.00              | MIN               | Clearance over host board at rear of module                          |

| J1  | 0.31              | MIN               | Height of standoff boss on front posts                               |

| K1  | 0.76              | ±0.12             | Height of front posts                                                |

| L1  | 31.75             | ±0.50             | Distance from rear post to front plane, less optical receptacle      |

|     |                   |                   | assembly                                                             |

| M1  | 30.23             | BASIC             | Distance from front to rear posts                                    |

| N1  | 13.72             | BASIC             | Distance between posts, side-to-side                                 |

| P1  | 1.14              | BASIC             | MegArray pin A1 location                                             |

| R1  | 18.16             | BASIC             | MegArray pin A1 location                                             |

| S1  | Ø3.63             | ±0.25             | Rear posts' diameter                                                 |

| T1  | THREAD            | _                 | 2-56 UNC-2B threads, minimum 3.50 mm deep                            |

| V1  | Ø1.30             | ±0.12             | Front posts' diameter                                                |

| W1  | Ø2.50             | ±0.35             | Diameter of standoff boss on front post                              |

| X1  | _                 |                   | Position of optical plane                                            |

| Y1  | _                 |                   | Position of optical plane                                            |

| Z1  | 16.00             | MAX               | Height of top of module, including optional vendor specific heatsink |

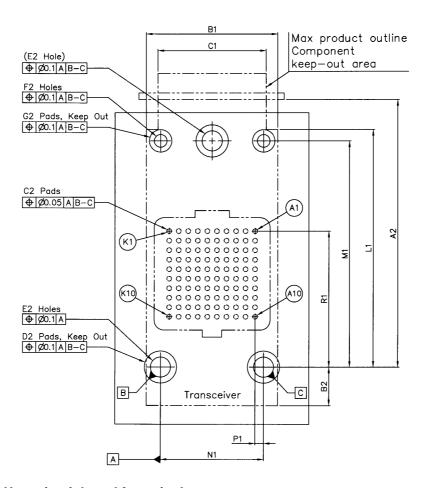

# 2 Circuit Board Footprint

Tolerancing per ASME Y-14.5-1994. All dimensions are in millimeters.

Figure 2 Host circuit board footprint layout

Table 2 Host circuit board footprint mechanical dimensions

| Key | Dimension | Tolerance | Comments                                                     |  |  |  |

|-----|-----------|-----------|--------------------------------------------------------------|--|--|--|

|     | [mm]      | [mm]      |                                                              |  |  |  |

| A2  | 35.31     | ±0.75     | Distance from rear post to inside surface of bezel           |  |  |  |

| B2  | 10.92     | MAX       | Distance from rear post to rear of module keep-out area      |  |  |  |

| C2  | Ø0.58     | ±0.05     | Diameter of pad in BGA pattern                               |  |  |  |

| D2  | Ø4.30     | MIN       | Diameter of keep-out pad for posts: two rear and one front   |  |  |  |

| E2  | Ø2.69     | ±0.12     | Diameter of hole for mounting screws: two rear and one front |  |  |  |

| F2  | Ø1.70     | ±0.12     | Diameter of hole for front post                              |  |  |  |

| G2  | Ø3.00     | MIN       | Diameter of keep-out pad for front post                      |  |  |  |

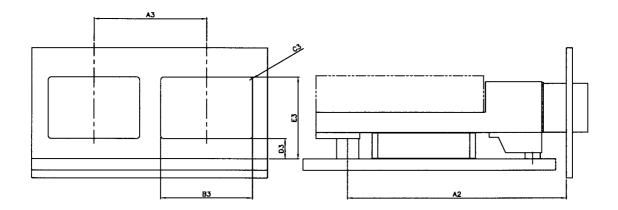

# 3 Host Frontplate Layout for Panel Accessed Modules

Tolerancing per ASME Y-14.5-1994. All dimensions are in millimeters.

Figure 3 Host frontplate layout

Table 3 Host frontplate dimensions

| Key | Dimension<br>[mm] | Tolerance<br>[mm] | Comments                                             |  |  |  |

|-----|-------------------|-------------------|------------------------------------------------------|--|--|--|

| A3  | 19.02             | MIN               | Center-to-center spacing for adjacent modules        |  |  |  |

| В3  | 15.70             | ±0.25             | Width of opening in frontplate                       |  |  |  |

| C3  | 0.50              | MAX               | Corner radius of opening in frontplate               |  |  |  |

| D3  | 3.60              | ±0.2              | Height from host PCB to bottom of frontplate opening |  |  |  |

| E3  | 13.40             | ±0.2              | Height from host PCB to top of frontplate opening    |  |  |  |

# 4 Transceiver Module Signals

The pluggable parallel optical transceivers shall use a 100 position FCI Meg Array receptacle (FCI PN: 84513-101) or equivalent electrical connector.

The modules shall use an industry standard MTP™(MPO) optical connector compliant with IEC 61754-7.

#### 4.1 Tranceiver Pad Assignments

Top of table toward front of module.

Table 4 Transceiver module pad assignment

|    | K          | J                   | Н                   | G                   | F         | E         | D         | С         | В         | Α         |

|----|------------|---------------------|---------------------|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 1  | Dоит00-    | VEE<br>Rx           | Douт03+             | VEE<br>Rx           | VEE<br>Rx | VEE<br>Tx | VEE<br>Tx | DIN03-    | VEE<br>Tx | DIN00+    |

| 2  | Dout00+    | VEE<br>Rx           | Dоит03-             | VEE<br>Rx           | VEE<br>Rx | VEE<br>Tx | VEE<br>Tx | DIN03+    | VEE<br>Tx | DIN00-    |

| 3  | VEE<br>Rx  | VEE<br>Rx           | VEE<br>Rx           | VEE<br>Rx           | VEE<br>Rx | VEE<br>Tx | VEE<br>Tx | Vee<br>Tx | Vee<br>Tx | VEE<br>Tx |

| 4  | Dout01+    | VEE<br>Rx           | Dout02-             | DNC                 | DNC       | DNC       | DNC       | DIN02+    | Vee<br>Tx | DIN01-    |

| 5  | Dout01-    | VEE<br>Rx           | Dout02+             | DNC                 | DNC       | DNC       | DNC       | DIN02-    | Vee<br>Tx | DIN01+    |

| 6  | VEE<br>Rx  | VEE<br>Rx           | VEE<br>Rx           | DNC                 | DNC       | DNC       | DNC       | Vee<br>Tx | Vee<br>Tx | VEE<br>Tx |

| 7  | Vссв<br>Rx | Vccb<br>Rx          | Vссв<br>Rx          | DNC                 | DNC       | DNC       | DNC       | Vcc<br>Tx | Vcc<br>Tx | Vcc<br>Tx |

| 8  | DNC        | Reserved<br>TBD MSA | Reserved<br>TBD MSA | Reserved<br>TBD MSA | [RX_EN]   | TX_DIS    | TX_EN     | DNC       | DNC       | DNC       |

| 9  | DNC        | Reserved<br>TBD MSA | Reserved<br>TBD MSA | SD                  | [SQ_EN]   | RESET*    | FAULT*    | DNC       | DNC       | DNC       |

| 10 | Vcca<br>Rx | Vcca<br>Rx          | VEE<br>Rx           | DNC                 | DNC       | DNC       | DNC       | VEE<br>Tx | Vcc<br>Tx | Vcc<br>Tx |

**TOP VIEW (Host Printed Circuit Board layout)**

#### 4.2 Transceiver MTP Connector

|     | Front view – MTP key is up      |  |  |  |  |  |  |  |  |  |  |

|-----|---------------------------------|--|--|--|--|--|--|--|--|--|--|

| Tx0 | Tx0 Tx1 Tx2 Tx3 Rx3 Rx2 Rx1 Rx0 |  |  |  |  |  |  |  |  |  |  |

|     | Host printed circuit board      |  |  |  |  |  |  |  |  |  |  |

#### 5 Definitions: Signals, Pad Functions, Posts

- DIN00+/- through DIN03+/- Transmitter differential data inputs for channels 0 through 3. Data inputs are CML compatible.

- TX\_DIS Transmitter Disable. Control input used to turn off the transmitter optical outputs. High Active. VCSEL array is off when High. Normal operation is enabled when Low and TX\_EN High. Internal pull-down

- TX\_EN Transmitter Enable. Control input used to enable the transmitter optical outputs. High Active. VCSEL array is off when Low. Normal operation is enabled when High and TX\_DIS Low. Internal pull-up.

- FAULT\* Transmitter Laser Fault. Status output indicating VCSEL driving condition faults on all channels. Low Active. One channel or more not functional when Low. Normal operation when High. Disables all channels when active, clear with Reset.

- RESET\* Transmitter Reset. Control input used to clear Fault. Low Active. Optical output is off when Low. Normal operation is enabled when High. Internal pull-up.

- DOUT00+/- through DOUT03+/- Receiver differential data outputs for channels 0 through 3. Data outputs are CML compatible.

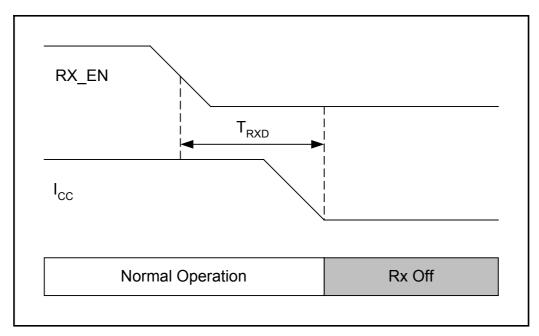

- RX\_EN Receiver Enable. Control input used to enable the receiver. High Active. Receiver is powered down when Low. Normal operation is enabled when High. Internal pull-up. (Optional)

- SD Signal Detect. Receiver status output indicating valid signal on all channels. High Active. High output indicates valid optical inputs on all channels. Low output state indicates loss of signal on at least one of the channels. Internal pull-up.

- SQ\_EN Squelch Enable. Control input used to enable squelch on the electrical output signal. High Active. When active, data out is squelched on any channels that have loss of incoming signal. Internal pull-up. (Optional)

- V<sub>EE</sub> Rx Receiver signal common. All receiver voltages are referenced to this potential unless otherwise stated. Directly connect these pads to the PC board receiver ground plane.

- V<sub>EE</sub> Tx Transmitter signal common. All transmitter voltages are referenced to this potential unless otherwise stated. Directly connect these pads to the PC board transmitter ground plane.

- DNC Do Not Connect. Do not connect to any electrical potential.

- V<sub>CCA</sub> Rx PIN preamplifier power supply rail

- V<sub>CCB</sub> Rx Receiver quantizer power supply rail

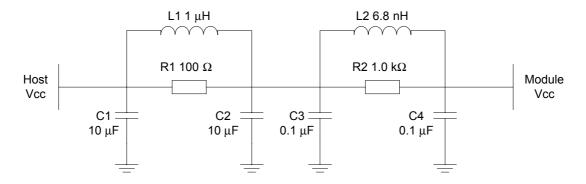

- $V_{\text{CCA}}$  Rx and  $V_{\text{CCB}}$  Rx can be connected to the same power supply. However, to insure maximum receiver sensitivity and minimize the impact of noise from the power supply, it is recommended to keep the power supplies separate and to use the recommended power supply filtering network on  $V_{\text{CCA}}$  Rx, see Figure 4.

- V<sub>CC</sub> Tx Transmitter power supply rail.

- Reserved TBD MSA Reserved for future MSA defined functions.

- Module Case Transceiver Case Common. Transceiver Case Common is electrically isolated from Transmitter Signal Common and Receiver Signal Common. Connection through mounting screw holes or frontplate whichever is applicable. Make the appropriate electrical connection for EMI shield integrity.

# 6 Transceiver Specifications

#### 6.1 General Specifications

| Parameter                       | Symbol            | Min   | Тур | Max   | Units      | Reference |

|---------------------------------|-------------------|-------|-----|-------|------------|-----------|

|                                 |                   |       |     |       |            |           |

| Power Supply Voltage            | $V_{CC}$          | 3.135 | 3.3 | 3.465 | V          |           |

| Operating Case Temperature      | T <sub>CASE</sub> | 0     |     | 80    | °C         |           |

| Signaling Rate (per channel)    | $f_D$             | 1     |     | 2.7   | GBd        | 1         |

| Control Input Voltage High      | V <sub>IH</sub>   | 2.0   |     |       | V          |           |

| Control Input Voltage Low       | V <sub>IL</sub>   |       |     | 0.8   | V          |           |

| Status Output Voltage High      | V <sub>OH</sub>   | 2.4   |     |       | V          |           |

| Status Output Voltage Low       | V <sub>OL</sub>   |       |     | 0.4   | V          |           |

| Data I/O DC Blocking Capacitors | C <sub>BLK</sub>  | 100   |     |       | nF         | 2         |

| Power Supply Noise              | PSN               |       |     | 200   | $mV_{p-p}$ | 3         |

Figure 4 Recommended power supply filter network for both transmitter and receiver

<sup>1</sup> Data patterns are to have maximum run lengths and DC balance shifts no worse than that of a Pseudo Random Bit Sequence of length  $2^{23}$ -1 (PRBS-23).

<sup>2</sup> DC blocking capacitors are required; if on PC board, a minimum value of 100 nF is recommended.

<sup>3</sup> Power supply noise is defined at the supply side of the recommended filter for all  $V_{CC}$  supplies over the frequency range of 500 Hz to 2700 MHz with the recommended power supply filter in place.

#### 6.2 Transmitter Specifications

All parameters below require  $T_{CASE}$  = 0 to 80 °C,  $V_{CC}$  = 3.3 V ± 5%, and  $f_D$  = 2.7 GBd.

| Parameter                                     | Symbol                 | Min | Max  | Units             | Reference |

|-----------------------------------------------|------------------------|-----|------|-------------------|-----------|

| Optical Parameters                            |                        |     |      |                   |           |

| Launch Power                                  | P <sub>OUT</sub>       | -8  | -2   | dBm               | 4         |

| Extinguished Output Power                     | P <sub>OFF</sub>       |     | -30  | dBm               |           |

| Extinction Ratio                              | ER                     | 6   |      | dB                |           |

| Center Wavelength                             | $\lambda_{\mathrm{C}}$ | 830 | 860  | nm                |           |

| Spectral Width                                | Δλ                     |     | 0.85 | nm <sub>rms</sub> |           |

| Relative Intensity Noise (OMA)                | RIN <sub>12</sub> OMA  |     | -116 | dB/Hz             | 5         |

| Output Rise Time (20-80%)                     | t <sub>RO</sub>        |     | 150  | ps                |           |

| Output Fall Time (20-80%)                     | t <sub>FO</sub>        |     | 150  | ps                |           |

| Total Jitter (pk-pk) - Tx Contributed         | TJ                     |     | 120  | ps                | 6         |

| Deterministic Jitter (pk-pk) - Tx Contributed | DJ                     |     | 50   | ps                |           |

| Channel-Channel Skew                          | t <sub>SK</sub>        |     | 100  | ps                | 7         |

| Electrical Parameters                         |                        |     |      |                   |           |

| Supply Current                                | I <sub>cc</sub>        |     | 150  | mA                |           |

| Differential Input Voltage Amplitude          | $ \Delta V_{IN} $      | 100 | 800  | mV                | 8         |

| Differential Input Impedance                  | Z <sub>IN</sub>        | 80  | 120  | Ω                 | 9         |

| Input Rise Time (20-80%)                      | t <sub>RE</sub>        |     | 160  | ps                |           |

| Input Fall Time (20-80%)                      | t <sub>FE</sub>        |     | 160  | ps                |           |

<sup>4</sup> The output optical power is compliant with IEC 60825-1:2001, Class 1M Accessible Emission Limits.

<sup>5</sup> Corresponds to a Relative Intensity Noise (RIN) of -120 dB/Hz.

<sup>6</sup> Total Jitter, TJ, equals TP1 to TP2 as defined in IEEE 802.3 Gigabit Ethernet Specification, clauses 38.2 and 38.6.

<sup>7</sup> Channel-Channel Skew is defined for the condition of equal amplitude, zero ps skew signals applied to the transmitter inputs.

<sup>8</sup> Differential Input Voltage,  $|\Delta V_{IN}|$ , is defined as the absolute value of the differential voltage between Din+ and Din-. Data inputs are CML compatible.

<sup>9</sup> Differential Input Impedance is measured between Din+ and Din-.

#### 6.3 Receiver Specifications

All parameters below require  $T_{CASE}$  = 0 to 80 °C,  $V_{CC}$  = 3.3 V ± 5%,  $f_D$  = 2.7 GBd and a termination load of 100  $\Omega$  differential at the electrical output.

| Parameter                             | Symbol             | Min   | Max | Units | Reference |

|---------------------------------------|--------------------|-------|-----|-------|-----------|

| Optical Parameters                    |                    |       |     |       |           |

| Receive Power (Average)               | P <sub>IN</sub>    | -16   | -2  | dBm   | 10        |

| Center Wavelength                     | λ <sub>C</sub>     | 830   | 860 | nm    |           |

| Return Loss                           | RL                 | 12    |     | dB    | 11        |

| Stressed Receiver Sensitivity         | P <sub>SS</sub>    | -11.7 |     | dBm   | 12, 13    |

| Channel-Channel Skew                  | t <sub>SK</sub>    |       | 100 | ps    | 14        |

| Signal Detect Asserted                | P <sub>SA</sub>    |       | -17 | dBm   |           |

| Signal Detect De-asserted             | P <sub>SD</sub>    | -31   |     | dBm   |           |

| Signal Detect Hysteresis              | $P_{SA}-P_{SD}$    | 0.5   |     | dB    |           |

| Electrical Parameters                 |                    |       |     |       |           |

| Supply Current                        | I <sub>CC</sub>    |       | 250 | mA    |           |

| Differential Output Voltage Amplitude | $ \Delta V_{OUT} $ | 250   | 400 | mV    | 15        |

| Stressed Receiver Eye Opening         | P <sub>SE</sub>    | 111   |     | ps    | 16        |

| Output Rise Time (20-80%)             | t <sub>RE</sub>    |       | 160 | ps    |           |

| Output Fall Time (20-80%)             | t <sub>FE</sub>    |       | 160 | ps    |           |

<sup>10</sup> Receive Power for a channel is measured for a BER of  $10^{-12}$  and worst case Extinction Ratio.  $P_{IN}(Min)$  is measured using a fast rise/fall time source with low RIN and adjacent channel(s) operating with incident power of 6 dB above  $P_{IN}(Min)$  specification.

<sup>11</sup> Return Loss is measured as defined in IEEE 802.3z Gigabit Ethernet Specification Section 38.5.

<sup>12</sup> The stressed receiver sensitivity is measured using PRBS  $2^{23}$ -1 pattern, 2.6 dB Inter-Symbol Interference, ISI, (Min), 30 ps Duty Cycle Dependent Deterministic Jitter, DCD DJ (Min) and 6 dB ER (ER Penalty = 2.2 dB). All channels not under test are receiving signals with an average input power of 6 dB above  $P_{IN}(Min)$  specification.

<sup>13</sup> The optional high bandwidth fiber (2000 MHz\*km), require the Stressed Receiver Sensitivity parameter to meet –12.5 dBm.

<sup>14</sup> Channel-Channel Skew is defined for the condition of equal amplitude, zero ps skew signals applied to the transmitter inputs.

<sup>15</sup> Differential Output Voltage,  $|\Delta V_{OUT}|$ , is defined as the absolute value of the differential voltage between Dout+ and Dout- and measured with a 100  $\Omega$  differential load connected between Dout+ and Dout-. Data outputs are CML compatible.

<sup>16</sup> The stressed receiver eye opening represents the eye at TP4 as defined in IEEE 802.3 clauses 38.2 and 38.6 (Gigabit Ethernet). The stressed receiver eye opening is measured using PRBS  $2^{23}$ -1 pattern, 2.6 dB ISI (Min), 30 ps DCD DJ (Min), 6 dB ER and an average input optical power of –11.2 dBm (0.5 dB above Minimum Stressed Receiver Sensitivity as defined in IEEE 802.3 clause 38.6). All channels not under test are receiving signals up to an average input power of 6 dB above  $P_{IN}(Min)$  specification.

#### 6.4 Timing Requirements of Control and Status Signals

The following figures and subsequent table show and tabulate the timing relationships of the status and control signals of the pluggable transceiver modules. As specified in the previous section, some of these signals are optional.

Figure 5 Transmitter FAULT\* signal timing diagram

Figure 6 Transmitter RESET\* signal timing diagram

Figure 7 Transmitter ENABLE and DISABLE signal timing diagram

Figure 8 Receiver Signal Detect timing diagram

Figure 9 Receiver ENABLE signal timing diagram

Table 5

Timing requirements of control and status signals

| Parameter             | Symbol            | Min | Тур | Max | Unit | Comment                                                                              |

|-----------------------|-------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------|

| FAULT* assert time    | T <sub>FA</sub>   |     |     | 100 | μs   | Time from occurance of a transmitter fault until the FAULT* signal goes active (Low) |

| FAULT* lasers off     | T <sub>FD</sub>   |     |     | 100 | μs   | Time from occurance of a transmitter fault to the lasers shutting off                |

| RESET* duration       | $T_TDD$           | 10  |     |     | μs   | Minimum hold time for RESET* active (Low) to clear a fault                           |

| RESET* de-assert time | T <sub>ON</sub>   |     | 33  | 100 | ms   | Time until data is valid after RESET* de-active (High)                               |

| TX_EN assert time     | T <sub>TEN</sub>  |     |     | 1   | ms   | Time until data is valid after TX_EN active (High)                                   |

| TX_DIS de-assert time | T <sub>TEN</sub>  |     |     | 1   | ms   | Time until data is valid after TX_DIS de-active (High)                               |

| SD assert time        | $T_{SD}$          |     | 50  |     | μs   | Time after valid data until SD is valid (High)                                       |

| SD de-assert time     | T <sub>LOS</sub>  |     | 50  |     | μs   | Time after data no longer valid until SD is de-active (Low)                          |

| RX_EN assert time     | T <sub>RXEN</sub> |     | 33  |     | ms   | Time until data is valid after RX_EN active (High)                                   |

| RX_EN de-assert time  | $T_RXD$           |     | 5   |     | μs   | Time after RX_EN de-active (Low) during which data is still valid                    |

#### 6.5 Link Length

The following table lists the minimum reach distance of the pluggable optical transceiver modules for different multi-mode fiber (MMF) types and bandwidths. Each case includes a maximum of 2 dB per channel connection loss for path cables and other connectors.

| Fiber Type             | Modal Bandwidth<br>@ 850 nm | Reach Distance<br>@ 2.5 Gbps | Reach Distance<br>@ 2.7 Gbps |

|------------------------|-----------------------------|------------------------------|------------------------------|

| [core / cladding µm]   | [MHz*km]                    | [m]                          | [m]                          |

| 62.5/125 MMF           | 200                         | 135                          | 115                          |

| 62.5/125 or 50/125 MMF | 400                         | 260                          | 220                          |

| 50/125 MMF             | 500                         | 300                          | 270                          |

| 50/125 MMF (Optional)  | 2000                        | 600                          | 500                          |

#### 6.5.1 Link Model Parameters

The link lengths above have been achieved with the following link model parameters.

| Parameter                         | Symbol          | Value | Unit       |

|-----------------------------------|-----------------|-------|------------|

| Mode partition noise k-factor     | k               | 0.3   |            |

| Modal noise                       | MN              | 0.3   | dB         |

| Dispersion slope parameter        | So              | 0.11  | ps/nm^2*km |

| Wavelength of zero dispersion     | Uo              | 1320  | nm         |

| Attenuation coefficient at 850 nm | $lpha_{\sf db}$ | 3.5   | dB/km      |

| Conversion factor                 | C1              | 480   | ns.MHz     |

| Q-factor [BER 10 <sup>-12</sup> ] | Q               | 7.04  |            |

| TP4 eye opening                   |                 | 0.3   | UI         |

| DCD allocation at TP3             | DCD DJ          | 0.08  | UI         |

| RMS baseline wander S.D.          | $\sigma_{BLW}$  | 0.025 |            |

| RIN coefficient                   | $k_{rin}$       | 0.70  |            |

| Conversion factor                 | c_rx            | 329   | ns.MHz     |

#### 6.5.2 Restricted Launch (Optional)

The transceiver would be guaranteed to meet the inner and outer requirements of encircled flux VCSEL launch specification defined in TIA/EIA-492AAAC 'Detailed Specification for 850 nm Laser Optimized 50  $\mu$ m Core Diameter/125  $\mu$ m Cladding Diameter, Class 1 a Graded Index Multimode Optical Fibers'.

- Encircled flux launch at (inner) 4.5 μm radius <= 30%

- Encircled flux launch at (outer) 19 μm radius >= 86%

# 7 Eye Safety

The maximum optical output power is specified to comply to Class 1M in accordance with IEC 60825-1:2001. In addition the transceiver complies with FDA performance standards for laser products except for deviations pursuant to Laser Notice No.50, dated July 26, 2001.